# User Guide of Pipeline CAMAC Controller with PC104plus Single Board Computer (CC/NET)

Yoshiji YASU, Eiji INOUE, Shuichi HARADA(1) and Haruyuki KYOO(2)

Online group, Institute of Particle and Nuclear Studies

> High Energy Accelerator Research Organization(KEK)

- (1) TOYO Corporation

- (2) Fird Corporation

November 2003

## Contents

| 1 | Intr | roduction                                                            | 1               |

|---|------|----------------------------------------------------------------------|-----------------|

|   | 1.1  | Overview of Pipeline CAMAC Controller                                | 1               |

|   |      | 1.1.1 Functionality                                                  | 1               |

|   |      | 1.1.2 Performance                                                    | 2               |

|   |      | 1.1.3 Pipeline Method: Why so fast?                                  | 2               |

|   | 1.2  | Organization                                                         | 4               |

| 2 | Har  | rdware Components                                                    | 1               |

|   | 2.1  | PC104plus Single Board Computer                                      | 1               |

|   | 2.2  | PCI control unit                                                     | 1               |

|   |      | 2.2.1 Architecture                                                   | 1               |

|   |      | 2.2.2 Components: Tx/Rx FIFOs, Tx/Rx PCI engines and PCI multiplexer | 3               |

|   | 2.3  | CAMAC control unit                                                   | 3               |

|   |      | 2.3.1 CAMAC Executor                                                 | 3               |

|   |      | 2.3.2 CAMAC Interrupter                                              | 3               |

|   |      | 2.3.3 DAQ Executor                                                   | 3               |

|   |      | 2.3.4 DAQ Interrupter                                                | 4               |

|   | 2.4  | CSP: a general purpose interconnect between PCI and CAMAC            | 4               |

|   |      | 2.4.1 Introduction                                                   | 4               |

|   | 2.5  | Front Panel                                                          | 5               |

|   |      | 2.5.1 LEDs                                                           | 5               |

|   |      | 2.5.2 Switches                                                       | 5               |

|   |      | 2.5.3 Trigger-Input and Busy-Out                                     | 5               |

|   |      | 2.5.4 Ethernet, USB, VGA and PS/2                                    | 5               |

|   | 2.6  | Power Consumption                                                    | 7               |

|   |      | 2.6.1 Power for CPU board                                            | 7               |

|   |      | 2.6.2 Power consumption of 6 V on CAMAC bus                          | 7               |

| 3 | Ope  | eration                                                              | 8               |

|   | 3.1  | PCI I/O registers                                                    | 8               |

|   |      | 3.1.1 Tx Data1 and Tx Data2 registers                                | 8               |

|   |      | 3.1.2 Tx Control register                                            | 8               |

|   |      |                                                                      | 10              |

|   |      | 0                                                                    | $10^{-1}$       |

|   |      | v                                                                    | $10^{-10}$      |

|   |      |                                                                      | $10^{-1}$       |

|   |      |                                                                      | $\frac{12}{12}$ |

|   |     | 3.1.8  | Rx Control register                                        |      | $1^{2}$      |

|---|-----|--------|------------------------------------------------------------|------|--------------|

|   |     | 3.1.9  | Rx Status register                                         |      | . 12         |

|   |     | 3.1.10 | Rx Memory Address register                                 |      | . 13         |

|   |     | 3.1.11 | Rx Preset Count and Rx Actual Count registers              |      | . 13         |

|   |     | 3.1.12 | Rx FIFO Count register                                     |      | . 14         |

|   |     | 3.1.13 | System register                                            |      | . 14         |

|   |     | 3.1.14 | Int Data1 and Int Data2 registers                          |      | . 14         |

|   |     | 3.1.15 | Int Control register                                       |      | . 15         |

|   |     | 3.1.16 | Int Status register                                        |      | . 15         |

|   |     | 3.1.17 | Int FIFO Count register                                    |      | . 15         |

|   | 3.2 | Frame  | Format                                                     |      | . 16         |

|   |     | 3.2.1  | Frame Header                                               |      | . 16         |

|   |     | 3.2.2  | Basic CAMAC function                                       |      | . 18         |

|   |     | 3.2.3  | CAMAC LAM Interrupt                                        |      | . 18         |

|   |     | 3.2.4  | DAQ function                                               |      | . 19         |

|   |     | 3.2.5  | DAQ Trigger Interrupt                                      |      | . 21         |

|   | 3.3 | Opera  | tion procedure                                             |      |              |

|   |     | 3.3.1  | PIO                                                        |      |              |

|   |     | 3.3.2  | DMA                                                        |      | . 22         |

|   |     | 3.3.3  | Interrupt                                                  |      |              |

|   | 3.4 | Specia | d CAMAC Functions to pipeline CAMAC controller             |      | . 22         |

| 4 | CA  | MAC 1  | Device Driver and the Library                              |      | 24           |

|   | 4.1 |        | ation                                                      |      |              |

|   |     | 4.1.1  | How to get the distribution kit                            |      |              |

|   |     | 4.1.2  | How to compile and load the device driver                  |      |              |

|   | 4.2 | Genera | al Purpose CAMAC Library                                   |      |              |

|   |     | 4.2.1  | Setup Functions                                            |      |              |

|   |     | 4.2.2  | CAMAC Functions                                            |      |              |

|   |     | 4.2.3  | CAMAC Single Action                                        |      | . 27         |

|   |     | 4.2.4  | Interrupt Handling                                         |      |              |

|   | 4.3 | CAMA   | AC Library dedicated to pipeline CAMAC controller          |      |              |

|   |     | 4.3.1  | CAMAC frame buffer structure                               |      |              |

|   |     | 4.3.2  | CAMAC/DAQ command frame generators                         |      | . 30         |

|   |     | 4.3.3  | CAMAC open/close                                           |      |              |

|   |     | 4.3.4  | PIO routines                                               |      | . 31         |

|   |     | 4.3.5  | Block I/O routines                                         |      | . 33         |

|   |     | 4.3.6  | Combined routine                                           |      |              |

|   |     | 4.3.7  | Interrupt handling routines for Trigger and LAM Interrupts |      | . 34         |

|   |     | 4.3.8  | CAMAC/DAQ reply frame extraction routines                  |      | . 36         |

|   | 4.4 | Examı  | ,                                                          |      |              |

|   |     | 4.4.1  | Tools                                                      |      | . 37         |

|   |     | 4.4.2  | Check programs                                             |      |              |

|   |     | 1. 1   |                                                            |      |              |

|   | 4.5 |        | amming                                                     |      |              |

|   | 4.5 |        |                                                            |      | . 42         |

|   | 4.5 | Progra | amming                                                     | <br> | . 42<br>. 42 |

|   |     | 4.5.4  | Interrupt handling                                          | 43 |

|---|-----|--------|-------------------------------------------------------------|----|

| 5 | Lin | ıx Sys | tem                                                         | 45 |

|   | 5.1 | -      | Installation using KNOPPIX CD including CAMAC utility       | 45 |

|   |     | 5.1.1  | How to get the distribution kit                             | 46 |

|   |     | 5.1.2  | How to install Linux system                                 | 46 |

|   | 5.2 | Applie | ation Software                                              | 46 |

|   |     | 5.2.1  | Simple remote access programs written in C language         | 47 |

|   |     | 5.2.2  | Remote Access program using Java Remote Method Invocation   |    |

|   |     |        | (JavaRMI)                                                   | 47 |

| 6 | Per | formar | ace                                                         | 50 |

|   | 6.1 | Enviro | nment and setup for the measurement                         | 50 |

|   | 6.2 | lmben  | ch for Linux system performance measurement                 | 50 |

|   |     | 6.2.1  | Timing issues                                               | 50 |

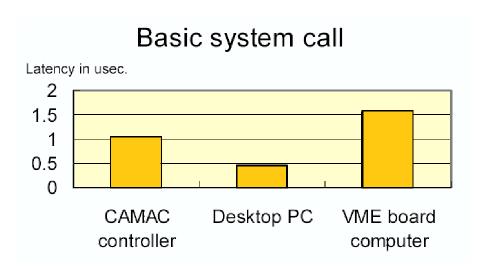

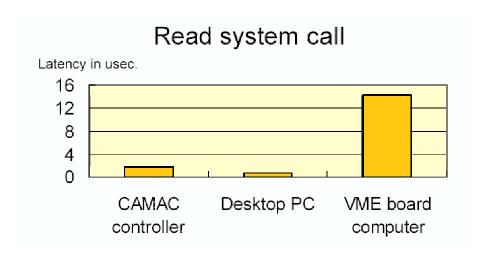

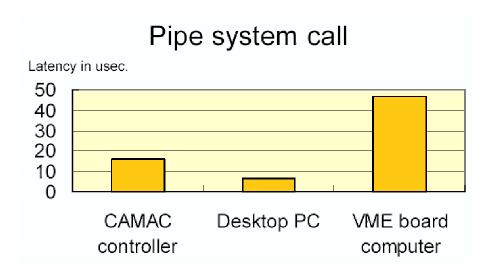

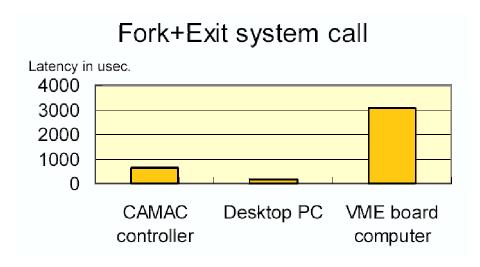

|   |     | 6.2.2  | Latency measurements                                        | 51 |

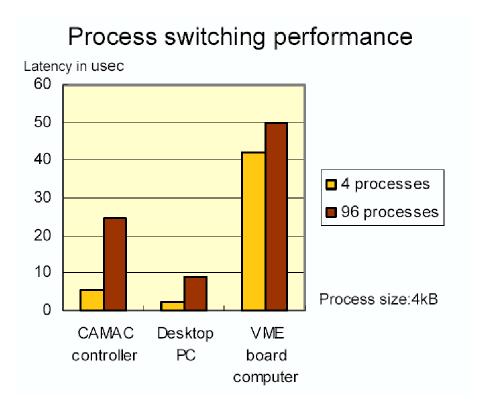

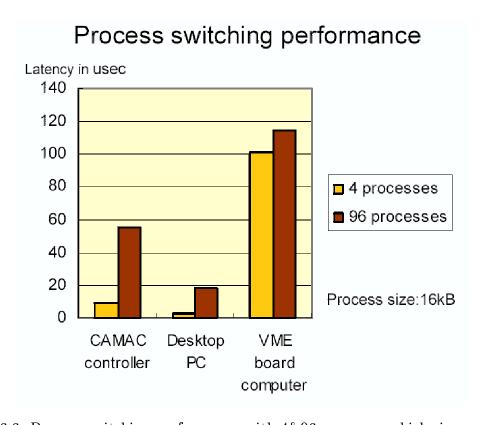

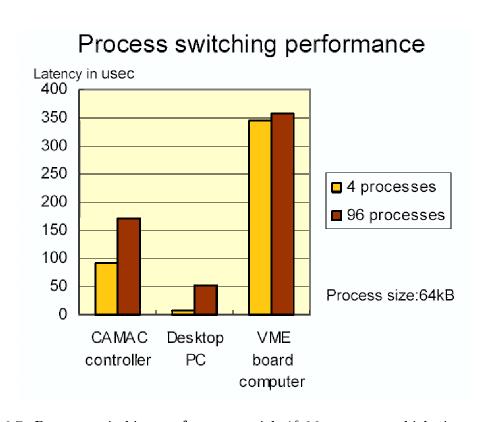

|   |     | 6.2.3  | Context switching performance                               | 53 |

|   | 6.3 | Other  | benchmark programs for Linux system performance measurement | 57 |

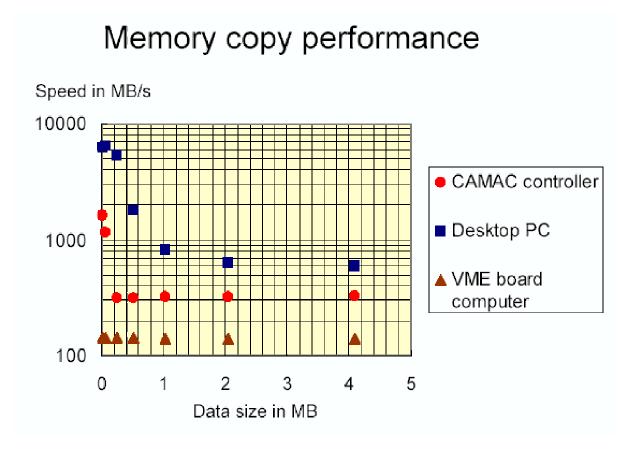

|   |     | 6.3.1  | Memory Copy Performance                                     | 57 |

|   |     | 6.3.2  | NETPERF                                                     | 57 |

|   | 6.4 | CAMA   | AC performance                                              | 59 |

|   |     | 6.4.1  | Performance of basic functions                              | 59 |

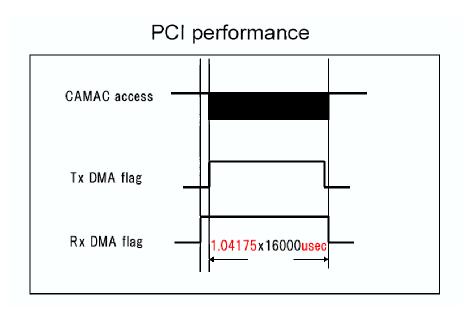

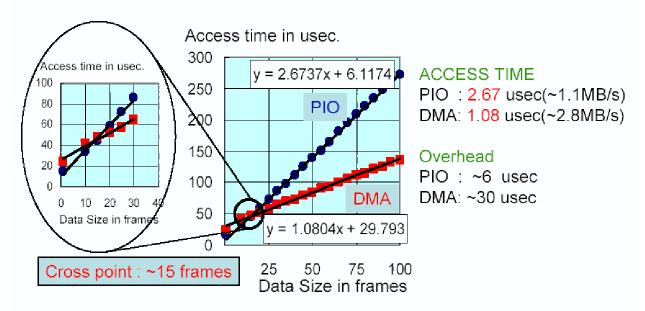

|   |     | 6.4.2  | Block transfer performance                                  | 60 |

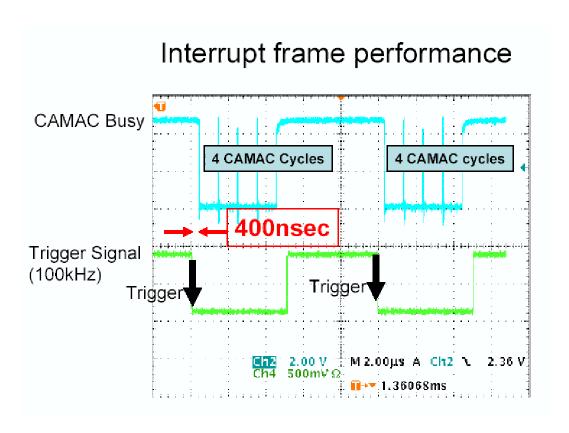

|   |     | 6.4.3  | Interrupt frame performance                                 | 60 |

|   |     | 6.4.4  | CAMAC performance with the CAMAC library                    | 62 |

|   | 6.5 | Applie | ation performance                                           | 62 |

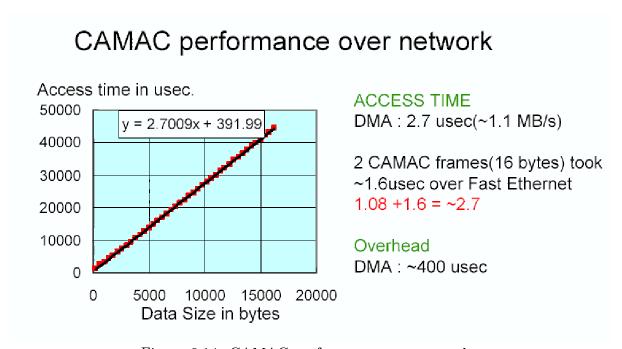

|   |     | 6.5.1  | CAMAC remote access program                                 | 62 |

## List of Tables

| 2.1  | CSP signals                                   | 5  |

|------|-----------------------------------------------|----|

| 2.2  | Power Consumption of the CPU board            | 7  |

| 2.3  | Power Consumption of 6 V on CAMAC bus         |    |

| 3.1  | PCI I/O register map                          | 9  |

| 3.2  | Tx Data1 and Tx Data2 registers               | 9  |

| 3.3  | Tx Control register                           | 10 |

| 3.4  | Tx Status register                            | 11 |

| 3.5  | Tx Memory Address register                    | 11 |

| 3.6  | Tx Preset and Actual Count registers          | 11 |

| 3.7  | Tx FIFO Count register                        |    |

| 3.8  | Rx Data1 and Rx Data2 registers               |    |

| 3.9  | Rx Control register                           | 12 |

| 3.10 | Rx Status register                            | 13 |

| 3.11 | Rx Memory Address register                    | 13 |

|      | Rx Preset and Actual Count registers          |    |

|      | Rx FIFO Count register                        |    |

|      | System register                               |    |

|      | Int Data1 and Int Data2 registers             |    |

|      | Int Control register                          |    |

|      | Int Status register                           | 15 |

|      | Int FIFO Count register                       | 16 |

|      | Frame Format                                  | 16 |

|      | Frame Header                                  | 16 |

|      | Selection of Operation                        |    |

|      | Frame Header Contents                         | 17 |

|      | Payload for Basic CAMAC command frame         | 18 |

|      | Payload for Basic CAMAC reply frame           |    |

|      | CAMAC status                                  |    |

|      | Payload for CAMAC LAM Interrupt reply frame   |    |

|      | Payload for Basic DAQ command frame           | 20 |

|      | DAQ control                                   | 20 |

|      | Payload for Basic DAQ reply frame             | 20 |

|      | DAQ Status                                    | 21 |

|      | Payload for DAQ Trigger Interrupt reply frame | 21 |

|      | Special CAMAC Function                        | 23 |

|      | •                                             |    |

| 11   | CAMAC frame buffer structure                  | 20 |

| 6.1 | Environment and setup for the performance measurement | 51 |

|-----|-------------------------------------------------------|----|

| 6.2 | Null system call time (in usec)                       | 52 |

| 6.3 | Process creation time (in usec)                       | 53 |

| 6.4 | Context switch times with 4 processes (in usec)       | 54 |

| 6.5 | Context switch times with 96 processes (in usec)      | 56 |

| 6.6 | I/O port access performance                           | 59 |

| 6.7 | performance of kernel routines                        | 59 |

| 6.8 | CAMAC performance                                     | 59 |

## List of Figures

| 1.1  | Configuration of Pipeline CAMAC Controller                              | 2  |

|------|-------------------------------------------------------------------------|----|

| 1.2  | Performance of Pipeline CAMAC Controller                                |    |

| 2.1  | pipeline CAMAC controller                                               | 2  |

| 2.2  | Block diagram of PCI control unit                                       |    |

| 2.3  | Block diagram of CAMAC control unit                                     |    |

| 2.4  | Front Panel of Pipeline CAMAC Controller                                |    |

| 3.1  | Frame formats of CAMAC command and reply                                | 17 |

| 3.2  | Frame formats of DAQ command and reply                                  | 19 |

| 5.1  | GUI for CAMAC                                                           | 49 |

| 6.1  | Latency of getppid system call                                          | 52 |

| 6.2  | Latency of read system call                                             | 52 |

| 6.3  | Latency of pipe system call                                             | 53 |

| 6.4  | Latency of fork&exit system call                                        | 54 |

| 6.5  | Process switching performance with 4&96 processes which size are 4KB .  | 55 |

| 6.6  | Process switching performance with 4&96 processes which size are 16KB . | 55 |

| 6.7  | Process switching performance with 4&96 processes which size are 64KB . | 56 |

| 6.8  | Memory Copy Performance                                                 | 57 |

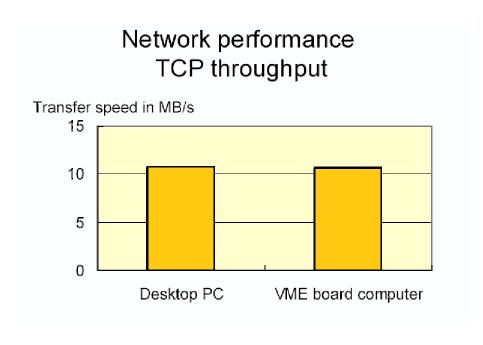

| 6.9  | TCP throughput                                                          | 58 |

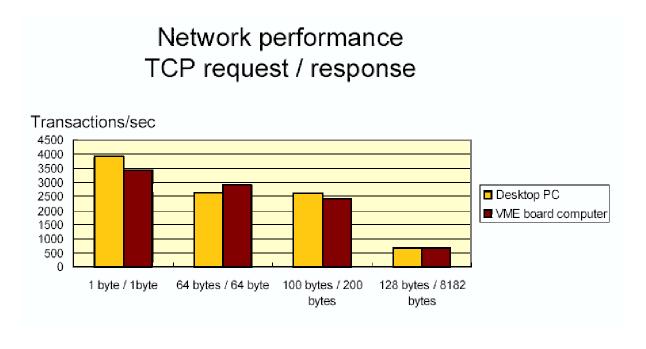

| 6.10 | TCP request & response                                                  |    |

|      | Block transfer performance                                              |    |

|      | Interrupt Frame Performance                                             |    |

|      | CAMAC performance with software library                                 |    |

| 6.14 | CAMAC performance over network                                          | 63 |

## Chapter 1

## Introduction

#### 1.1 Overview of Pipeline CAMAC Controller

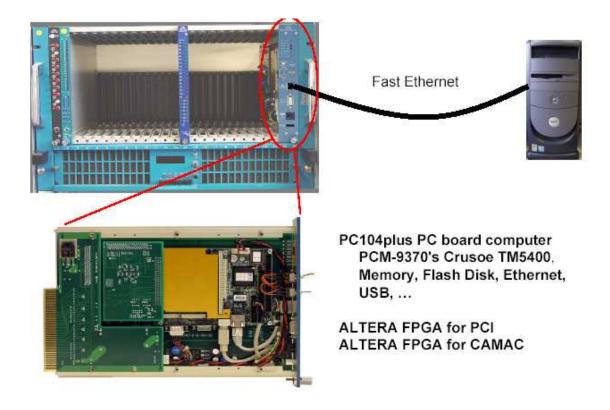

CAMAC[1] is a IEEE standard electronics and still used in High Energy and Nuclear Physics experiments. Lots of CAMAC controller were developed so far, but the pipeline CAMAC controller is an epoch-making controller because the throughput achieves approximately up to 3 MB/s with 24-bit data. The controller occupies 2 slots(station 24,25) in a CAMAC crate. The controller is located in the crate shown in Figure 1.1. It consists of a PC104Plus-based single board computer, PCI interface (PCI control unit) and CAMAC interface (CAMAC control unit). The PC104Plus is a standard PCI specification for embedded systems[2] and the low-power board computer includes a flash disk with IDE interface, Fast Ethernet, USB and so on. The PCI and CAMAC interfaces consist of a ALTERA FPGA[3], respectively. The controller also has a DAQ function for event numbering. The signal handling of trigger-input and busy-out are implemented while the event count can be read out.

Linux system[4, 5] can run on the pipeline CAMAC controller while the device driver and the library[6, 7, 8] are also provided.

The pipeline CAMAC controller and the software are developed by KEK[9], TOYO[10] and Fird[11].

#### 1.1.1 Functionality

There are a CAMAC Executor, a CAMAC LAM Handler (CAMAC Interrupter), a DAQ Executor and a DAQ Trigger Handler (DAQ Interrupter) in the pipeline CAMAC controller. The Executors accept a packet including at least a command frame or more from CPU via PCI, execute them and then send reply frames to CPU. The Handlers generate a packet including a reply frame and then send to CPU. When LAM or Trigger interrupt occurs during the executors processes a packet, the generation of interrupt reply frame will be postponed. After the packet is processed, the interrupt reply frame will be sent.

The pipeline CAMAC controller can execute CAMAC command with small overhead continuously by receiving the command frames from a computer memory and sending the reply frames to the computer memory. The controller also includes a DAQ function for event numbering. The NIM signal of trigger input and busy out can be handled while the event count can be read out.

Figure 1.1: Configuration of Pipeline CAMAC Controller

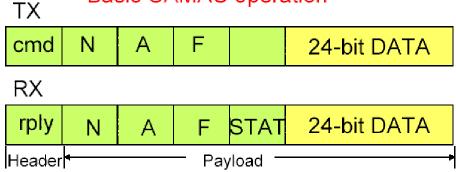

The size of command and reply frames is 64-bit. It consists of 8-bit header and 56-bit payload. The payload for basic CAMAC command frame contains CAMAC station number N, CAMAC sub-address A, CAMAC function F and data to be written if necessary. That for the reply frame additionally contains CAMAC status such as Q & X and read data if the CAMAC function is 'read'. That for CAMAC LAM includes 24-bit LAM pattern and that for DAQ Trigger includes 32-bit event count. That for DAQ Executor can clear busy-out signal while the signal disables next event trigger.

#### 1.1.2 Performance

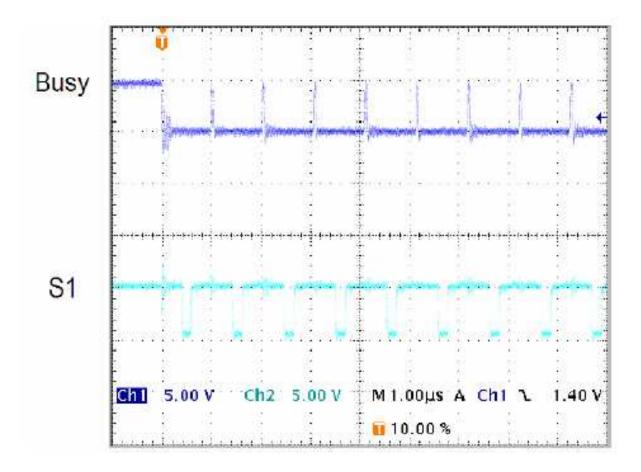

The pipeline CAMAC controller can execute a CAMAC access in 1 usec + small overhead (40 nsec), that is, the throughput is approximately 3 MB/sec with 24-bit data. Figure 1.2 shows the performance of the controller. An unit of mesh in the Figure is 1 usec. CAMAC Busy and CAMAC S1 signals are shown.

#### 1.1.3 Pipeline Method: Why so fast?

From historical point of view, CPU speed of PC and the Bus speed are getting faster and faster. However, the actual CAMAC access speed of the controllers so far is slow and far from maximum CAMAC speed, 3 MB/sec. There is a reason why it is so slow. It is already proved that pipeline method is useful for speed up on DAQ system. Lots of architectures related to pipeline method were developed in 1990s. However, no CAMAC controller adopted the pipeline method so far. The key point is to adopt a true pipeline from CAMAC command in CPU memory to the result (e.g., readout data) in CPU memory.

Figure 1.2: Performance of Pipeline CAMAC Controller

Some CAMAC controller partially adopted the pipeline method using a list processing[12], but it was not the true pipeline. Thus, the throughput did not achieve maximum CAMAC speed 3 MB/sec because the pipeline was destroyed at some point. The pipeline CAMAC controller realized the true pipeline.

The architecture of the pipeline CAMAC controller is completely different from that of old style of CAMAC controller so far. Thus, the operation of the pipeline CAMAC controller is also different from that of the old CAMAC controller. For the operation on the old CAMAC controller, N (station number), A (sub-address) and F (function) are put into an I/O register in the CAMAC controller and then the go bit of the register is set for starting the operation. Then, the status of the completion is checked and the data are read. After that, next operation of CAMAC command will start. The old CAMAC controller does not adopt the pipeline method. The pipeline CAMAC controller adopts the truly pipeline method. The pipeline method enabled the controller maximum speed of CAMAC, approximately up to 3 MB/sec with 24-bit data. On one hand, the pipeline CAMAC controller sends multiple command frames, which include N, A, F and data if necessary, via Tx I/O registers in the PCI control unit. On the other hand, the controller receives multiple reply frames, which also includes N, A, F, status(Q and X) and data if necessary, via Rx I/O registers in the PCI control unit. The operations to Tx and Rx are done concurrently. If DMA is used, the throughput reaches maximum speed. The Figure 1.2 is the timing of CAMAC Busy and CAMAC S1 signals when the DMA starts. DMA function is provided on old CAMAC controller, but the function is limited such as Address-scan, Q-stop and so on. For the pipeline CAMAC controller, any operation to CAMAC are executed in DMA mode. There is no limitation. From DMA point of view, the pipeline CAMAC controller is also completely different from old CAMAC controller.

#### 1.2 Organization

The readers of this guide may not read all of chapters. This section introduces the contents of all chapters in the guide briefly. Thus, the readers can jump to the chapter they need.

This chapter 1 shows the overview of pipeline CAMAC controller. They should read this chapter first to understand the pipeline CAMAC controller.

The chapter 2 introduce the hardware components. The chapter describes the detail of three components, PC104-Plus board computer, PCI control unit and CAMAC control unit. There are also the descriptions of the front panel and the power consumption.

The chapter 3 describes not only the PCI operation but also the frame format of CAMAC/DAQ command/reply. The PCI registers and the bit assignment are shown. The special CAMAC functions are also explained. If the readers like to understand the detail of how to operate the registers, read the section of operation procedure.

The chapter 4 explains how to get the distribution kit of CAMAC device driver and the library, how to install the driver and the library, the usage and the examples. It describes the detail of calling sequence of the CAMAC libraries while there are a general purpose CAMAC library and a dedicated CAMAC library for the pipeline CAMAC controller.

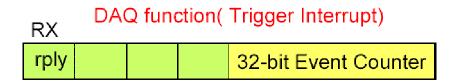

The chapter 5 describes Linux system and the applications running on the pipeline CAMAC controller. The chapter introduces how to recover the Linux system although a Linux system tailored by KEK will be pre-installed into a compact flash disk at purchase of the pipeline CAMAC controller. Two application programs are shown. One is remote

CAMAC library and another is a WEB-based CAMAC executor. When the remote CAMAC library is used, a CAMAC program running on the pipeline CAMAC controller (the board computer) can run on remote computer without any modification. By using WEB-based CAMAC executor, a simple CAMAC operation can be done on a WEB navigator such as Internet Explorer.

The chapter 6 shows the results of the performance measurement. It includes Linux system performance measured by a benchmark program **Imbench**, **netperf** and so on. From the results from **Imbench**, Latency of operating system entry, process creation costs and context switching costs are shown. **netperf** provides TCP throughput performance and TCP response / request performance. Memory copy performance is measured by a simple program. The CAMAC performance is also included in the results. It consists of performance of basic functions, block transfer performance, interrupt frame performance and CAMAC performance with the software library. From application point of view, CAMAC remote access program is evaluated.

This user guide is available in the URL[13].

## Chapter 2

## **Hardware Components**

The pipeline CAMAC controller is located into 24th and 25th slots of CAMAC crate. It mainly consists of a PC104Plus Single Board Computer, a PCI control unit and a CAMAC control unit. Figure 2.1 shows the side view of pipeline CAMAC controller called CC/NET. There are four boards as the components. The left side board including CAMAC card edge connector in the front is called D board. It includes DC-DC converter and CAMAC line driver. The center board including gold plate in the front is called C board. It is the board computer. The smallest board in the front is called A board, which is connected to the C board via PC104Plus PCI bus[2]. It is the PCI control unit. The rear board is called B board, which is connected to the A board via a general purpose interconnect called CSP[14]. The CAMAC control unit consists of the D board and the B board.

#### 2.1 PC104plus Single Board Computer

The board computer is Advantech PCM-9370[15], 3.5" (145 mm x 102 mm) Transmeta Crusoe 500 MHz processor Single Board Computer including TM5400 processor, 310 MB memory, two IDE UltraDMA 33 mode up to 33MB/sec, LCD/CRT controller, 10/100 Mbps Ethernet controller, two 1.1 compliant USB ports, mini-din connector for keyboard, PS/2 mouse and so on. The board computer also support an Embedded PCI protocol, PC/104-Plus.

#### 2.2 PCI control unit

The A board includes a ALTERA FLEX10KE100 FPGA. On one hand, the board connects to CPU board via 4x30 (120-pin) 2mm pitch stack-through connector for PC104plus PCI. On the other hand, the board also connects to CAMAC control unit via 2x40 (80-pin) TX14 series connector for a general purpose interconnect called CSP[14].

#### 2.2.1 Architecture

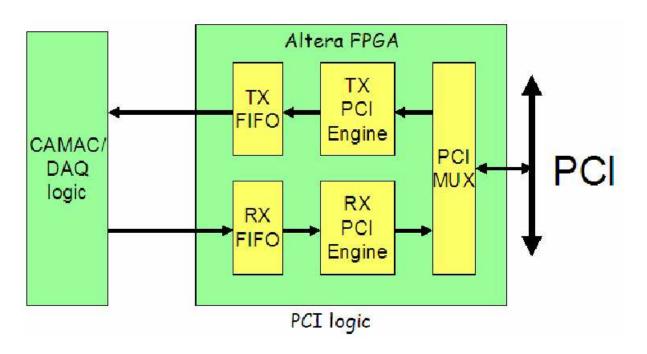

The block diagram of PC control unit is shown in Figure 2.2. There are, Tx/Rx FIFO, Tx/Rx PCI engines and PCI multiplexer for Tx/Rx. Tx and Rx PCI engines work independently while PCI multiplexer manages the PCI usage for Tx and Rx PCI engines.

Figure 2.1: pipeline CAMAC controller

Figure 2.2: Block diagram of PCI control unit

# 2.2.2 Components: Tx/Rx FIFOs, Tx/Rx PCI engines and PCI multiplexer

Tx/Rx FIFOs have the depth of 256 with 32-bit width each. Tx/Rx PCI engines have two modes, master and slave. The slave means PCI slave which the PCI interface becomes at the operation of PCI registers from CPU. In master mode, the PCI interface can transfer data from/to memory in computer without CPU intervention. Thus, master mode not only reduces CPU usage but also realizes fast transfer in comparison with the slave mode.

The Tx PCI engine receives a least a command frame via PCI bus and then sends it to the Tx FIFO. The Tx FIFO sends the command frame to a CAMAC executor via the CSP. The Rx FIFO engines receives a least a reply frame via the CSP and then sends it to the Rx PCI engine. The Rx PCI engine send the reply frame to PCI. The PCI multiplexer shares the PCI usage with Tx/Rx PCI engines. Thus, Tx/Rx PCI engines can work independently.

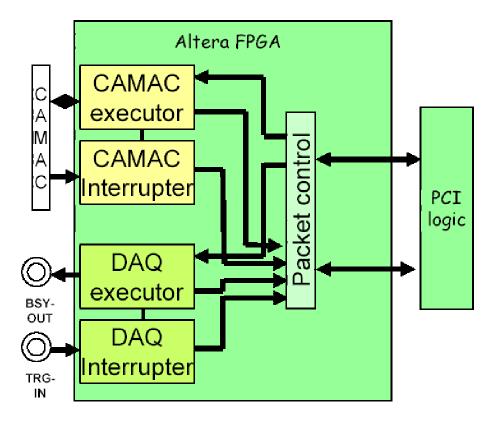

#### 2.3 CAMAC control unit

The unit in the Figure 2.3 includes the B board located into 25th CAMAC station and the D board located into 24th CAMAC station. The B board is a main board of CAMAC control unit, which contains ALTERA FLEX10KE50 FPGA. The B board is connected to the D board via 2x40 (80-pin) TX14 series connector. The D board contains DC-DC converter for the C board and the line driver for CAMAC bus.

The FPGA includes basic CAMAC execution by CAMAC Executor, CAMAC LAM handling by CAMAC Interrupter, execution of DAQ functions by DAQ Executor and DAQ trigger handling by DAQ Interrupter as the functions.

#### 2.3.1 CAMAC Executor

The executor receives CAMAC command frames from the PCI control unit and then executes CAMAC cycles. It sends CAMAC reply frames as the result to the PCI control unit via the packet control circuit.

#### 2.3.2 CAMAC Interrupter

The interrupter generates a LAM interrupt frame as CAMAC reply frame when an interrupt occurs on a CAMAC module. The reply frame is sent to the PCI control unit via the packet control circuit.

#### 2.3.3 DAQ Executor

The executor receives DAQ command frames from the PCI control unit and then executes the DAQ functions. It sends the result frames as DAQ reply frames to the PCI control unit via the packet control circuit.

Figure 2.3: Block diagram of CAMAC control unit

#### 2.3.4 DAQ Interrupter

The interrupter generates a DAQ trigger interrupt frame as DAQ reply frame when a DAQ trigger is input from TRIG-IN LEMO connector. The reply frame is sent to REPLY FIFO via the packet control circuit.

# 2.4 CSP: a general purpose interconnect between PCI and CAMAC

The PCI control unit and CAMAC control unit are connected by the interconnect. The interconnect is designed in general. It can handle simple packet transfer. A packet contains multiple frames. For an example, the frame size for CAMAC is 8 bytes. This means 4 cycles of the interconnect is necessary for a CAMAC frame.

#### 2.4.1 Introduction

When ReadyToWrite and ReadyToRead signals are asserted, data can be sent and received. A packet transfer begins at this moment. The transmitter should write data and the receiver should read it at next clock when EnableToSendPacket and EnableToReceivePacket signals are both asserted. When ReadyToWrite or ReadyToRead signal is deasserted, a packet transfer should be terminated. When EnableToWrite or EnableToRead signal is deasserted, a packet transfer should be paused.

Table 2.1: CSP signals

| I/O Signal name        | Description                                       |

|------------------------|---------------------------------------------------|

| ReadyToWrite           | Ready to write a packet or start writing a packet |

| ${f Enable To Write}$  | Enable to write data in a packet                  |

| ReadyToRead            | Ready to read or start reading a packet           |

| ${\it Enable To Read}$ | Enable to read data in a packet                   |

| Clock                  | Up to 25MHz                                       |

| Data                   | 16bits                                            |

| Data width             | 1 means 16-bit width and 0 means 8-bit width      |

| Tx Information         | 4 bits for transmitter                            |

| Rx Information         | 4 bits for receiver                               |

#### 2.5 Front Panel

Figure 2.4 shows a front panel of the Pipeline CAMAC controller.

#### 2.5.1 LEDs

There are several LEDs. The CPU LED is used for indicating status of CAMAC control unit. If the LED blinks, CAMAC control unit is not ready. Thus, a flag SYS\_READY in System register should be set. The BUSY LED is direct reflection of CAMAC Busy signal. The NO-X and NO-Q LEDs mean final states of CAMAC X and CAMAC Q, respectively. If CAMAC X or CAMAC Q is not set, the NO-X or NO-Q is light. The L-SUM LED is light when one of CAMAC modules issues LAM and the LAM is enabled. The I LED means final state of CAMAC Inhibit. The IE LED is light when the interrupt of the controller is enabled.

#### 2.5.2 Switches

There are two toggle switches. One is for setting CAMAC Online and Offline. Another is for generating CAMAC Z and CAMAC C.

There is a small push-button for reseting the Pipeline CAMAC controller. The reset makes the power down/up.

#### 2.5.3 Trigger-Input and Busy-Out

Two LEMO connectors of NIM signals for Trigger Input and Busy Out are used for event numbering of DAQ.

#### 2.5.4 Ethernet, USB, VGA and PS/2

There are Fast Ethernet connector, VGA connector, PS/2 connector and USB connector. The USB is master device, not target device. Thus, the pipeline CAMAC controller can not be handled via the USB.

Figure 2.4: Front Panel of Pipeline CAMAC Controller

Table 2.2: Power Consumption of the CPU board

| Condition         | Power consumption |

|-------------------|-------------------|

| booting time      | 16.8 W - 14.4 W   |

| idle time         | 9.6 W - 7.2W      |

| CAMAC access time | 14.4 W - 12.0 W   |

| Disk access time  | 16.8 W - 14.4 W   |

Table 2.3: Power Consumption of 6 V on CAMAC bus

| Condition                                     | Power consumption |

|-----------------------------------------------|-------------------|

| idle time                                     | 1.8 - 2.4 W       |

| CAMAC access time ( data pattern = 0 )        | 6.0 - 6.6 W       |

| CAMAC access time ( data pattern = 0xFFFFFF ) | 6.6 - 7.2 W       |

#### 2.6 Power Consumption

The power consumption of the pipeline CAMAC controller depends on the running condition. The CPU board (C board) consumes lots of power. Its power is supplied via DC-DC converter from 24 V to 6 V on the D board. Thus, 24 V of CAMAC power supply should be monitored. On the other hand, CAMAC line driver consumes the power of 6 V on CAMAC bus. Thus, 6 V of CAMAC power supply should be also monitored. It is assumed that there is no graphic display. There were two CAMAC modules. One is the pipeline CAMAC controller. Another one is a switch register.

#### 2.6.1 Power for CPU board

At booting time of Linux system, the current of 0.7-0.6 A flowed. This means that the power of 14.4 W to 16.8 W was consumed. Table 2.2 shows the power consumption depended on the condition. The power consumption in the table 2.2 except CAMAC access time only includes that of CPU board, not the switch register module because the module does not use 24V.

#### 2.6.2 Power consumption of 6 V on CAMAC bus

There were two CAMAC modules. One is the pipeline CAMAC controller. Another one is a switch register. The power consumption in the table 2.3 is total power consumption including both modules.

### Chapter 3

## Operation

#### 3.1 PCI I/O registers

There are three kinds of registers. One is for Tx and another is for Rx. The other is system register. Those registers are located in PCI I/O space and the size of those registers is 32-bit.

In programmed I/O (PIO), Data1 and Data2 registers for Tx and Rx are used for sending command frames and receiving reply frames, respectively. FIFO count register contains number of data in longword(4bytes). For an example, Rx FIFO count register is used for getting the number of data to be transferred.

In block I/O (DMA), Address register is used for pointing to address of kernel command/reply frame buffers and preset count register represents the number of frames in quadword(8 bytes) to be transferred. After the transfer, actual count register contains the number of frames in quadword(8 bytes) transferred actually. Control register and status register contains control and status information related to interrupt and DMA.

System register is used by system administrator.

Those registers are summarized in Table 3.1.

#### 3.1.1 Tx Data1 and Tx Data2 registers

Data1 and Data2 registers for Tx are used for sending command frames in Programmed I/O mode. As the size of command frame is 64-bit, lower 32-bit corresponds to Data1 register and upper 32-bit corresponds to Data2 register. Table 3.2 shows the format. When the upper data is written into Data2 register, 64-bit command frame will be sent to CAMAC. If data in Data1 register is used again, next command frame will be sent by only writing data to Data2 register.

#### 3.1.2 Tx Control register

Tx Control register contains control information related to interrupt and DMA. Whenever Tx FIFO is full, full-FIFO interrupt will occur if TC\_INT\_ENABLE\_FULL\_FIFO bit is set. Packet-end interrupt will occur only when Tx actual count register reaches to Tx present count register if TC\_INT\_ENABLE\_PKT\_END bit is set. When TC\_CLR\_FIFO bit is set, Tx FIFO in PCI control unit will be zero. Each bit assignment is shown in Table 3.3. The register can be read and written.

Table 3.1: PCI I/O register map

| I/O offset address | Register name | Description                |

|--------------------|---------------|----------------------------|

| 00h                | TxData1       | Tx data1 register          |

| 04h                | TxData2       | Tx data2 register          |

| 08h                | TxControl     | Tx control register        |

| 0Ch                | TxStatus      | Tx status register         |

| 10h                | TxAddress     | Tx address register        |

| 14h                | TxPresetCount | Tx preset count register   |

| 18h                | TxActualCount | Tx actual count register   |

| 1Ch                | TxFifoCount   | Tx FIFO count register     |

| 20h                | RxData1       | Rx data1 register          |

| 24h                | RxData2       | Rx data2 register          |

| 28h                | RxControl     | Rx control register        |

| 2Ch                | RxStatus      | Rx status register         |

| 30h                | RxAddress     | Rx memory address register |

| 34h                | RxPresetCount | Rx preset count register   |

| 38h                | RxActualCount | Rx actual count register   |

| 3Ch                | RxFifoCount   | Rx FIFO count register     |

| 40h                | System        | System register            |

| 60h                | IntData1      | Int data1 register         |

| 64h                | IntData2      | Int data2 register         |

| 68h                | IntControl    | Int control register       |

| 6Ch                | IntStatus     | Int status register        |

| 7Ch                | IntFifoCount  | Int FIFO count register    |

Table 3.2: Tx Data1 and Tx Data2 registers

| Bit assignment | =                                  |

|----------------|------------------------------------|

| D31D00         | 32-bit data used in Programmed I/O |

Table 3.3: Tx Control register

| Bit assignment | Bit name                | Description                 |

|----------------|-------------------------|-----------------------------|

| D31D28         |                         | 0(not used)                 |

| D27            |                         | 0 (not used)                |

| D26            | TC_INT_ENABLE_FORCE_END | Enable Force-end interrupt  |

| D25            | TC_INT_ENABLE_FULL_FIFO | Enable full-FIFO interrupt  |

| D24            | TC_INT_ENABLE_PKT_END   | Enable Packet-end interrupt |

| D23D20         |                         | 0(not used)                 |

| D19            |                         | 0 (not used)                |

| D18            | TC_INT_CLR_FORCE_END    | Clear Force-end interrupt   |

| D17            | TC_INT_CLR_FULL_FIFO    | Clear full-FIFO interrupt   |

| D16            | TC_INT_CLR_PKT_END      | Clear Packet-end interrupt  |

| D15D12         |                         | 0(not used)                 |

| D11D08         |                         | 0(not used)                 |

| D07D04         |                         | 0(not used)                 |

| D03D02         |                         | 0 (not used)                |

| D01            | TC_CLR_FIFO             | Clear Tx FIFO               |

| D00            | TC_SRT_DMA              | Start DMA                   |

#### 3.1.3 Tx Status register

Tx Status register contains status information related to interrupt and DMA. When the Tx/Rx information is zero, the communication via CSP has no problem while non-zero of the information means communication error occurs. The Status register is read-only. The detail is summarized in Table 3.4.

#### 3.1.4 Tx Memory Address register

In DMA, Tx Memory Address register is used for pointing to address of kernel command frame buffer to be transferred.

#### 3.1.5 Tx Preset Count and Tx Actual Count registers

In DMA, Tx Preset Count register represents the number of command frames to be transferred. Tx Actual Count register contains the number of frames transferred actually. The maximum size of those registers are shown in Table 3.6, but the maximum number is limited by operating system. In Linux, maximum size of kernel buffer which is allocated in a continuous memory, is 128 KB. This means 16K frames can be sent at once. Therefore, the maximum size is 14-bit for Linux.

#### 3.1.6 Tx FIFO Count register

Tx FIFO Count register represents the actual number of data in Tx FIFO. The unit is 32-bit, not 64-bit. The depth of FIFO is 256 for 128 command frames. Thus, the maximum size is 8-bit shown in Table 3.7.

Table 3.4: Tx Status register

| Bit assignment | Bit name         | Description                                 |

|----------------|------------------|---------------------------------------------|

| D31D28         | TS_RX_INFO       | Rx information                              |

| D27D24         | TS_TX_INFO       | Tx information                              |

| D23D20         |                  | 0(not used)                                 |

| D19            |                  | 0(not used)                                 |

| D18            | TS_INT_FORCE_END | When Force-end interrupt occurred, 1.       |

| D17            | TS_INT_FULL_FIFO | When full-FIFO interrupt occurred, 1.       |

| D16            | TS_INT_PKT_END   | When Packet-end interrupt occurred, 1.      |

| D15D12         |                  | 0(not used)                                 |

| D11            |                  | 0(not used)                                 |

| D10            | TS_FULL_FIFO     | indicating Tx FIFO is full.                 |

| D09            | TS_HALFFULL_FIFO | indicating Tx FIFO is half-full.            |

| D08            | TS_EMPTY_FIFO    | indicating Tx FIFO is empty.                |

| D07D04         |                  | 0(not used)                                 |

| D03D02         |                  | 0(not used)                                 |

| D01            | TS_TIMEOUT_FRAME | No CAMAC response (in PIO)                  |

| D00            | TS_DONE_FRAME    | A frame was successfully processed.(in PIO) |

Table 3.5: Tx Memory Address register

| Bit assignment | Description           |

|----------------|-----------------------|

| D31D00         | 32-bit Memory address |

Table 3.6: Tx Preset and Actual Count registers

| Bit assignment | Description                      |

|----------------|----------------------------------|

| D31D00         | 24-bit Counter (actually 14-bit) |

Table 3.7: Tx FIFO Count register

| Bit assignment | Description   |

|----------------|---------------|

| D31D00         | 8-bit Counter |

Table 3.8: Rx Data1 and Rx Data2 registers

| Bit assignment | Description                        |

|----------------|------------------------------------|

| D31D00         | 32-bit data used in programmed I/o |

Table 3.9: Rx Control register

| Bit assignment | Bit name                   | Description                             |

|----------------|----------------------------|-----------------------------------------|

| D31D30         |                            | 0(not used)                             |

| D29            | RC_INT_ENABLE_FORCE_END    | Enable Force-end interrupt              |

| D28            | RC_INT_ENABLE_PRESET_FIFO  | Enable Preset interrupt                 |

| D27            | RC_INT_ENABLE_FULL_FIFO    | Enable full-FIFO interrupt              |

| D26            | RC_INT_ENABLE_HALFFULL_PKT | Enable half size Packet-end interrupt   |

| D25            | RC_INT_ENABLE_PKT_END      | Enable Packet-end interrupt             |

| D24            | RC_INT_ENABLE_INPUT_FRAME  | Enable first frame input interrupt      |

| D23D22         |                            | 0(not used)                             |

| D21            | RC_INT_CLR_FORCE_END       | Clear Force-end interrupt               |

| D20            | RC_INT_CLR_PRESET_FIFO     | Clear Preset interrupt                  |

| D19            | RC_INT_CLR_FULL_FIFO       | Clear full-FIFO interrupt               |

| D18            | RC_INT_CLR_HALFFULL_PKT    | Clear half size of Packet-end interrupt |

| D17            | RC_INT_CLR_PKT_END         | Clear Packet-end interrupt              |

| D16            | RC_INT_CLR_INPUT_FRAME     | Clear first frame input interrupt       |

| D15D012        |                            | 0(not used)                             |

| D11D08         |                            | 0(not used)                             |

| D07D04         |                            | 0(not used)                             |

| D003D02        |                            | 0(not used)                             |

| D01            | RC_CLR_FIFO                | Clear Rx FIFO                           |

| D00            | RC_SRT_DMA                 | Start DMA                               |

#### 3.1.7 Rx Data1 and Rx Data2 registers

Data1 and Data2 registers shown in Table 3.8 for Rx are used for receiving reply frames after sending command frames. When Data1 register is read, 64-bit reply frame will be stored into Data1 and Data2 registers. Data1 and Data2 registers contain lower 32-bit and upper 32-bit, respectively.

#### 3.1.8 Rx Control register

Rx Control register contains control information related to interrupt and DMA. Whenever Rx FIFO is full, full-FIFO interrupt will occur if TC\_INT\_ENABLE\_FULL\_FIFO bit is set. Packet-end interrupt will occur only when Rx actual count register reaches to Rx present count register if TC\_INT\_ENABLE\_PKT\_END bit is set. When TC\_CLR\_FIFO bit is set, Rx FIFO in PCI control unit will be zero. Table 3.9 summaries them.

#### 3.1.9 Rx Status register

Rx Status register contains status information related to interrupt and DMA. The Status register is read-only. The detail is summarized in Table 3.10.

Table 3.10: Rx Status register

| Bit assignment | Bit name            | Description                                         |

|----------------|---------------------|-----------------------------------------------------|

| D31D28         | RS_RX_INFO          | Rx information                                      |

| D27D24         | RS_TX_INFO          | Tx information                                      |

| D23D22         |                     | 0(not used)                                         |

| D21            | RS_INT_FORCE_END    | When Force-end interrupt occurred, 1.               |

| D20            | RS_INT_PRESET_FIFO  | When Preset interrupt occurred, 1.                  |

| D19            | RS_INT_FULL_FIFO    | When full-FIFO interrupt occurred, 1.               |

| D18            | RS_INT_HALFFULL_PKT | When half size of Packet-end interrupt occurred, 1. |

| D17            | RS_INT_PKT_END      | When Packet-end interrupt occurred, 1.              |

| D16            | RS_INT_INPUT_FRAME  | When first frame input interrupt occurred, 1.       |

| D15D12         |                     | 0(not used)                                         |

| D11            |                     | 0(not used)                                         |

| D10            | RS_FULL_FIFO        | indicating Rx FIFO is full.                         |

| D09            | RS_HALFFULL_FIFO    | indicating Rx FIFO is half-full.                    |

| D08            | RS_EMPTY_FIFO       | indicating Rx FIFO is empty                         |

| D07D04         |                     | 0(not used)                                         |

| D03D01         |                     | 0(not used)                                         |

| D00            | RS_TIMEOUT_FRAME    | Timeout in PIO                                      |

Table 3.11: Rx Memory Address register

| Bit assignment | Description           |

|----------------|-----------------------|

| D31D00         | 32-bit Memory address |

#### 3.1.10 Rx Memory Address register

In DMA, Rx Memory Address register is used for pointing to address of kernel reply frame buffer to be transferred.

#### 3.1.11 Rx Preset Count and Rx Actual Count registers

In DMA, Rx Preset Count register represents the number of reply frames to be transferred. Rx Actual Count register contains the number of frames transferred actually. The maximum size of those registers are shown in Table 3.12, but the maximum number is limited by operating system. In Linux, maximum size of kernel buffer which is allocated in a continuous memory, is 128 KB. This means 16K frames can be sent at once. Therefore, the maximum size is 14-bit for Linux.

Table 3.12: Rx Preset and Actual Count registers

| Bit assignment | Description                      |

|----------------|----------------------------------|

| D31D00         | 24-bit Counter (actually 14-bit) |

Table 3.13: Rx FIFO Count register

| Bit assignment | Description   |

|----------------|---------------|

| D31D00         | 8-bit Counter |

Table 3.14: System register

| Bit assignment | Bit name             | Description                    |

|----------------|----------------------|--------------------------------|

| D31            | SYS_READY            | CAMAC ready state              |

| D30            | SYS_RESET            | reset PCI and CAMAC            |

| D29D28         |                      | 0 (not used)                   |

| D27D24         | SYS_CAMAC_FRAME_SIZE | frame size in 2**N (read-only) |

| D23D00         |                      | 0 (not used)                   |

#### 3.1.12 Rx FIFO Count register

Rx FIFO Count register represents the actual number of data in Rx FIFO. The unit is 32-bit, not 64-bit. The depth of FIFO is 256 for 128 reply frames. the maximum size is 8-bit shown in Table 3.13.

#### 3.1.13 System register

System register shown in Table 3.14 is used by system administrator. After power up, LED indicating system ready is blinking. When SYS\_READY flag is set, the LED continues to be light. This means CAMAC controller can be used. If some trouble occurs and CAMAC controller hangs up, SYS\_RESET flag is useful for resetting CAMAC controller. It is a reset without power off/on and resets the FPGAs of PCI and CAMAC. The frame size of command and reply is 64-bit, namely, 8 bytes. SYS\_CAMAC\_FRAME\_SIZE represents the size as 2\*\*N. Thus, the value should be 3. It is read-only.

#### 3.1.14 Int Data1 and Int Data2 registers

Data1 and Data2 registers for Int are used for receiving interrupt reply frames in Programmed I/O mode. As the size of command frame is 64-bit, lower 32-bit corresponds to Data1 register and upper 32-bit corresponds to Data2 register. Table 3.15 shows the format. When Data1 register is read, 64-bit reply frame will be stored into Data1 and Data2 registers.

Table 3.15: Int Data1 and Int Data2 registers

| Bit assignment | Description                        |

|----------------|------------------------------------|

| D31D00         | 32-bit data used in Programmed I/O |

Table 3.16: Int Control register

| Bit assignment | Bit name      | Description                     |

|----------------|---------------|---------------------------------|

| D31D28         |               | 0(not used)                     |

| D27D25         |               | 0 (not used)                    |

| D24            | IC_INT_ENABLE | Enable interrupt for LAM & TRIG |

| D23D20         |               | 0(not used)                     |

| D19D17         |               | 0 (not used)                    |

| D16            | IC_INT_CLR    | Clear interrupt for LAM & TRIG  |

| D15D12         |               | 0(not used)                     |

| D11D08         |               | 0(not used)                     |

| D07D04         |               | 0(not used)                     |

| D03D02         |               | 0 (not used)                    |

| D01            | IC_CLR_FIFO   | Clear Int FIFO                  |

| D00            |               | 0 (not used)                    |

Table 3.17: Int Status register

| Bit assignment | Bit name         | Description                       |

|----------------|------------------|-----------------------------------|

| D31D28         |                  | 0(not used)                       |

| D27D24         |                  | 0(not used)                       |

| D23D20         |                  | 0(not used)                       |

| D19D17         |                  | 0(not used)                       |

| D16            | IS_INT           | When an interrupt occurred, 1.    |

| D15D12         |                  | 0(not used)                       |

| D11            |                  | 0(not used)                       |

| D10            | IS_FULL_FIFO     | indicating Int FIFO is full.      |

| D09            | IS_HALFFULL_FIFO | indicating Int FIFO is half-full. |

| D08            | IS_EMPTY_FIFO    | indicating Int FIFO is empty.     |

| D07D04         |                  | 0(not used)                       |

| D03D01         |                  | 0(not used)                       |

| D00            | IS_TIMEOUT_FRAME | Timeout in PIO                    |

#### 3.1.15 Int Control register

Int Control register contains control information related to LAM & TRIG interrupt. The interrupt will occur when an interrupt reply frame comes into and IC\_INT\_ENABLE bit is set. When IC\_CLR\_FIFO bit is set, Int FIFO will be zero. Each bit assignment is shown in Table 3.16. The register can be read and written.

#### 3.1.16 Int Status register

Int Status register contains status information related to LAM & TRIG interrupt. The Status register is read-only. The detail is summarized in Table 3.17.

#### 3.1.17 Int FIFO Count register

Int FIFO Count register represents the actual number of data in Int FIFO. The unit is 32-bit, not 64-bit. The depth of FIFO is 256 for 128 command frames. Thus, the maximum

Table 3.18: Int FIFO Count register

| Bit assignment | Description   |

|----------------|---------------|

| D31D00         | 8-bit Counter |

Table 3.19: Frame Format

| D63D56                | D55D00            |  |

|-----------------------|-------------------|--|

| Frame Header (8 bits) | Payload (56 bits) |  |

size is 8-bit shown in Table 3.18.

#### 3.2 Frame Format

There are two types of frame, namely, command frame and reply frame. The command frame is sent to CAMAC from memory in computer via PCI bus while the reply frame is generated at CAMAC and then stored into memory in computer via PCI bus. The frame shown in Table 3.19 consists of the frame header and the payload. The size of the header is a byte or 8 bits while that of the payload is 7 bytes or 56 bits. The 64-bit frame are divided into two 32-bit data. The lower 32-bit data (D31..D00) corresponds to Data1 register and first 32-bit data in 32-bit data array. The upper 32-bit data (D63..D32) corresponds to Data2 register and second 32-bit data in 32-bit data array. This means the data format is represented in so-called little endian.

#### 3.2.1 Frame Header

A frame includes a frame header of a byte shown in Table 3.20. A packet can include at least one or more frames. The CC\_SPKT bit should be set for the start frame in a packet. The CC\_EPKT bit should be set for the end frame in a packet. When both the bits are set, the packet has a single frame. For the other frame, both the bits should be reset.

CC\_SEL bits chooses the operation in Table 3.21.

Table 3.22 shows all types of frame header.

Table 3.20: Frame Header

| Bit assignment | Bit name | Description                  |

|----------------|----------|------------------------------|

| D63            | CC_FIXED | always 1                     |

| D62            | CC_SPKT  | 1 if start frame in a packet |

| D61            | CC_EPKT  | 1 if end frame in a packet   |

| D60D59         | CC_SEL   | select operation             |

| D58D56         |          | 0 (not used)                 |

Table 3.21: Selection of Operation

| Bit 60 | Bit 59 | Operation                       |

|--------|--------|---------------------------------|

| 0      | 0      | Basic CAMAC operation           |

| 0      | 1      | CAMAC LAM Interrupt operation   |

| 1      | 0      | Basic DAQ operation             |

| 1      | 1      | DAQ Trigger Interrupt operation |

Table 3.22: Frame Header Contents

| Operation   | Start Frame | Normal Frame | End Frame | Packet Frame |

|-------------|-------------|--------------|-----------|--------------|

| Basic CAMAC | 0xC0        | 0x80         | 0xA0      | 0xE0         |

| CAMAC LAM   | -           | -            | -         | 0xE8         |

| Basic DAQ   | 0xD0        | 0x90         | 0xB0      | 0xF0         |

| DAQ TRIG    | -           | -            | =         | 0xF8         |

#### **CAMAC Frame Format**

64-bit fixed-length

Basic CAMAC operation

N:station, A:sub-address, F:function, STAT:status(Q,X,...)

Read: data(tx) has no meaning. Write: data(rx) has no meaning.

NDT: data(tx) and data(rx) have no meaning.

Figure 3.1: Frame formats of CAMAC command and reply

Table 3.23: Payload for Basic CAMAC command frame

| Bit assignment | Bit name    | Description          |

|----------------|-------------|----------------------|

| D55D48         | CCEXE_N     | CAMAC station number |

| D47D40         | CCEXE_A     | CAMAC sub-address    |

| D39D32         | CCEXE_F     | CAMAC function       |

| D31D24         |             | 0 (not used)         |

| D23D00         | CCEXE_WDATA | Data to be written   |

Table 3.24: Payload for Basic CAMAC reply frame

| Bit assignment | Bit name    | Description          |

|----------------|-------------|----------------------|

| D55D48         | CCEXE_N     | CAMAC station number |

| D47D40         | CCEXE_A     | CAMAC sub-address    |

| D39D32         | CCEXE_F     | CAMAC function       |

| D31D24         | CCEXE_STAT  | CAMAC status         |

| D23D00         | CCEXE_RDATA | Read Data            |

#### 3.2.2 Basic CAMAC function

Figure 3.1 shows frame formats of CAMAC command and reply. It also includes CAMAC Interrupt reply frame. For the basic CAMAC function, the command frame consists of **cmd** as the frame header, station number **N**, sub-address **A**, function **F** and 24-bit data **24-bit DATA** while the reply frame consists of **reply** as the frame header, station number **N**, sub-address **A**, function **F**, status **STAT** and 24-bit data **24-bit DATA**. Table 3.23 and 3.24 show the contents of payloads for the command frame and the reply frame, respectively.

Table 3.25 shows the contents of CAMAC status in the reply frame.

#### 3.2.3 CAMAC LAM Interrupt

Figure 3.1 shows the frame format of the CAMAC LAM interrupt reply frame. It consists of **reply** as the frame header and **24-bit LAM pattern**. If the bit 0 of the LAM pattern is set, it means that the CAMAC module at the CAMAC station 1 generates a LAM

Table 3.25: CAMAC status

| Bit assignment | Bit name           | Description                        |

|----------------|--------------------|------------------------------------|

| D31            | CCEXE_STAT_FSTC    | Fast Cycle mode                    |

| D30            |                    | 0 (not used)                       |

| D29            | CCEXE_STAT_LSUM    | indicating LAM exists              |

| D28            | CCEXE_STAT_IE      | indicating LAM interrupt is enable |

| D27            |                    | 0 (not used)                       |

| D26            | CCEXE_STAT_INHIBIT | indicating CAMAC INHIBIT is set    |

| D25            | CCEXE_STAT_X       | CAMAC X                            |

| D24            | CCEXE_STAT_Q       | CAMAC Q                            |

Table 3.26: Payload for CAMAC LAM Interrupt reply frame

| Bit assignment | Bit name      | Description      |

|----------------|---------------|------------------|

| D55D24         |               | 0 (not used)     |

| D23D00         | CCLAM_PATTERN | Read LAM pattern |

#### **DAQ Frame Format**

64-bit fixed-length

DAQ function( read event counter)

OPCD : DAQ operation code (clear event count, clear busy-out...)

STAT: status (busy-out...)

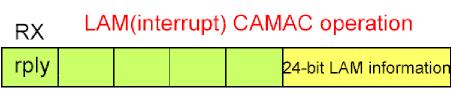

Figure 3.2: Frame formats of DAQ command and reply

interrupt while that at the station 23 generates the interrupt if the bit 22 is set.

#### 3.2.4 DAQ function

Figure 3.2 shows frame formats of DAQ command and reply. It also includes DAQ Trigger Interrupt reply frame. For the DAQ function, the command frame consists of **cmd** as the frame header and a control byte **OPCD**. The reply frame consists of **reply** as the frame header, a DAQ control byte **OPCD**, a DAQ status byte **STAT** and **32-bit Event Counter**. Table 3.27 and 3.29 show the contents of payloads for the command frame and the reply frame, respectively.

Table 3.28 shows the contents of a DAQ control byte. When the value 2 is set, the event counter becomes zero. After enabling the DAQ trigger interrupt by setting 3 into the value, the event counter will increment if the interrupt is input from TRIG-IN LEMO connector at the front panel of the pipeline CAMAC controller. At the moment,

Table 3.27: Payload for Basic DAQ command frame

| Bit assignment | Bit name    | Description      |

|----------------|-------------|------------------|

| D55D48         | DAQEXE_CTRL | DAQ Control bits |

| D47D40         |             | 0 (not used)     |

| D39D00         |             | 0 (not used)     |

Table 3.28: DAQ control

| Value of OPCD |                      | Description                                  |

|---------------|----------------------|----------------------------------------------|

| 0x00          | DAQEXE_CTRL_READ     | Read Event Counter                           |

| 0x01          | DAQEXE_CTRL_CLRBSY   | Clear Busy-Out signal                        |

| 0x02          | DAQEXE_CTRL_CLRCNT   | Clear Event Counter                          |

| 0x03          | DAQEXE_CTRL_ENABLE   | Enable DAQ trigger interrupt                 |

| 0x04          | DAQEXE_CTRL_DISABLE  | Disable DAQ trigger interrupt (default)      |

| 0x05          | DAQEXE_CTRL_PLSOUT   | Enable output pulse at BSY-OUT connector     |

| 0x06          | DAQEXE_CTRL_NOFRAME  | Disable generating interrupt frame (default) |

| 0x0A          | DAQEXE_CTRL_WAITTRIG | Wait for a trigger interrupt                 |

the Busy-Out signal will be also generated at BUSY-OUT LEMO connector at the front panel. After that, the DAQ trigger interrupt does not occur even if the interrupt is input. To enable next interrupt, Busy-Out should be reset by setting 1 into the value.

If DAQEXE\_CTRL\_PLSOUT is set, the behavior of the signal generation at at BSY-OUT connector will change. When a DAQ trigger occurs, Busy-Out signal is not generated. Instead, a output pulse will be generated when DAQEXE\_CTRL\_CLRBSY bit is set. The pulse width is 40 nsec.

The aim of this mode is as follows; If the normal mode is used, BUSY-OUT signal will be generated and used for veto to next trigger. However, the timing of the trigger input and the BUSY-OUT slightly change. For arranging the timing precisely, another veto signal will be used instead of the BUSY-OUT signal in normal mode. For setting the veto off, this mode is used. When clearing BUSY-OUT, a 40 nsec pulse will be generated. It sets the veto off.

A DAQ status **DAQEXE\_STAT\_TRIGIN** indicates the existence of a DAQ trigger input. The bit will be set when the trigger is input even if the trigger is not enabled.

Table 3.29: Payload for Basic DAQ reply frame

| Bit assignment | Bit name     | Description        |

|----------------|--------------|--------------------|

| D55D48         | DAQEXE_CTRL  | DAQ Control bits   |

| D47D40         |              | 0 (not used)       |

| D39D32         | DAQEXE_STAT  | DAQ Status bits    |

| D31D00         | DAQEXE_COUNT | Read Event Counter |

Table 3.30: DAQ Status

| Bit assignment | Bit name             | Description              |

|----------------|----------------------|--------------------------|

| D39D36         |                      | 0 (not used)             |

| D35            | DAQEXE_STAT_PLSOUT   | Pulse-out mode           |

| D34            | DAQEXE_STAT_TRIGIN   | DAQ trigger input        |

| D33            | DAQEXE_STAT_ENTRIGIN | Enable Trigger interrupt |

| D32            | DAQEXE_STAT_BSY      | Busy-Out                 |

Table 3.31: Payload for DAQ Trigger Interrupt reply frame

| Bit assignment | Bit name     | Description   |

|----------------|--------------|---------------|

| D55D32         |              | 0 (not used)  |

| D31D00         | DAQINT_COUNT | Event Counter |

#### 3.2.5 DAQ Trigger Interrupt

Figure 3.2 shows frame formats of DAQ trigger interrupt reply frame. Table 3.31 shows the contents of the payload. The reply frame consists of **reply** as the frame header and the **32-bit event counter**.

#### 3.3 Operation procedure

In the following sub-section, basic operation procedures of PIO, DMA and Interrupt to CPU are described. They do not explain real programs used in the device driver, but just show how to manipulate the PCI registers briefly.

#### 3.3.1 PIO

For PIO, Data1 and Data2 registers for Tx and Rx are used for the data path. The Status and FifoCount registers for Tx and Rx are used for the control path. It is assumed that TxFifoCount and RxFifoCount are zero. This means there is no frame in the TxFIFO and the RxFIFO. The lower 32-bit word of command frame should be put into TxData1 register first. At the moment, the command frame is not sent to the CAMAC control unit. When upper 32-bit word of the command frame is put into TxData2 register, the command frame will be sent to CAMAC via CSP. If the transfer to CAMAC is done successfully, TS\_DONE\_FRAME bit in TxStatus register will be set. Otherwise, TS\_TIMEOUT\_FRAME will be set. This means there is no CAMAC response. After the CAMAC execution, the reply frame will be stored into the RxFIFO in the PCI control unit. At the moment, the contents of RxFifoCount will be a value 2. This means there is a reply frame in the RxFIFO. For the read-out, RxData1 register should be read first. It includes the lower 32-bit word of reply frame. At the same time, the upper 32-bit word of the reply frame will be latched into the RxData2 register. When the data are read out, RxFifoCount will be decremented by 2. Thus, the upper 32-bit word can be read from the RxData2 register anytime. When the RxFIFO is empty and the RxData1 register is

read, RS\_TIMEOUT\_FRAME bit in the RxStatus register will be set. This means the operation failed.

#### 3.3.2 DMA

There are several registers related to DMA operation to pipeline CAMAC controller. The physical addresses of data buffers in Linux kernel are set into Address registers for Tx and Rx. The frame counts are set into PresetCount registers for Tx and Rx. Control registers for Tx and Rx are used to start the DMA operation, by setting TC\_SRT\_DMA bit in TxControl register and RC\_SRT\_DMA bit in RxControl register. It is assumed that TxFifoCount and RxFifoCount are zero. The following procedure is efficient for the DMA operation. The DMA operation for Rx should start first. At the moment, nothing happens because there is no reply frame in the RxFIFO. After starting the DMA, do not wait for the completion of the DMA. Instead, Tx DMA operation should start next. After the Tx DMA operation starts, command frames will be sent to CAMAC control unit. the control unit executes the command frames and then sends the reply frames to PCI control unit. As the result, the reply frames will be sent to Linux kernel buffer as soon as they are stored into the RxFIFO, because Rx DMA operation already starts.

#### 3.3.3 Interrupt

There are two groups of interrupt sources. One is for DMA operations. Another is for external interrupt sources. Enabling, disabling and clearing the interrupts are done on Control registers for Tx, Rx and Int while the Status registers shows current status of the interrupt sources.

There are lots of interrupt sources for the DMA operation. An important interrupt is packet end interrupt. The interrupt occurs when the PresetCount register exhausts or the value becomes zero. The related bits in TxControl register are TC\_INT\_ENABLE\_PKT\_END bit in TxControl register for enabling the packet end interrupt of Tx and TC\_CLR\_PKT\_END bit in the register for clearing it. To disable the interrupt, TC\_INT\_ENABLE\_PKT\_END bit should be reset. The related bits in Rx Control register are similar to that in Tx Control register.

For external interrupt sources, the interrupt occurs when a reply frame comes into the IntFIFO first after the contents of the IntFifoCount register is zero. When IC\_INT\_ENABLE bit in IntControl register is set and an interrupt reply frame comes into the IntFIFO, the interrupt occurs.

# 3.4 Special CAMAC Functions to pipeline CAMAC controller

There are several CAMAC functions to CAMAC controller in Table 3.32. At Power-on reset, those conditions are following. CAMAC Inhibit is set. Interrupt to CPU is disabled. Fast Cycle is disabled. All bits in LAM Enable register are reset.

Fast Cycle mode ignores CAMAC S2 timing. When the mode is set, the CAMAC cycle becomes 0.72 usec instead of 1.04 usec. Many CAMAC modules can work without

Table 3.32: Special CAMAC Function

| Function         | Description               |

|------------------|---------------------------|

| N(25).A(0).F(24) | Clear CAMAC Inhibit       |

| N(25).A(0).F(26) | Set CAMAC Inhibit         |

| N(25).A(1).F(24) | Disable Interrupt to CPU  |

| N(25).A(1).F(26) | Enable Interrupt to CPU   |

| N(25).A(2).F(24) | Disable Fast Cycle        |

| N(25).A(2).F(26) | Enable Fast Cycle         |

| N(25).A(0).F(16) | Generate CAMAC C          |

| N(25).A(0).F(17) | Generate CAMAC Z          |

| N(25).A(1).F(0)  | Read LAM Enable register  |

| N(25).A(1).F(16) | Write LAM Enable register |

$\operatorname{CAMAC}$  S2 timing, but it is invalid operation for CAMAC protocol. The mode should be used carefully.

## Chapter 4

# CAMAC Device Driver and the Library

The CAMAC device driver is developed for only the pipeline CAMAC controller. There are two kinds of CAMAC library developed for the controller. One is a general purpose CAMAC library and a CAMAC library dedicated to the pipeline CAMAC controller.

#### 4.1 Installation

The CAMAC device driver and the library are pre-installed at the purchase of the CAMAC controller. The following instruction is not necessary if the Linux system is not destroyed. The instruction is provided for the recovery process.

#### 4.1.1 How to get the distribution kit

The device driver and the library is available at the following URLs.

- KEK online group : http://www-online.kek.jp/~ yasu/Parallel-CAMAC/

- TOYO corporation: http://www.toyo.co.jp/daq/index.html

#### 4.1.2 How to compile and load the device driver

Make a device driver and test programs.

The major number of the device is assumed to be 70. Thus, If it is not convenient,

Makefile file should be modified.

```

% cd /home/toyo/camac

% make clean; make

```

• Make the device files.

This makes a device file in /dev directory. The name is pcc0.

```

% su

# make device

```

• install the device driver in Linux kernel.

```

# make install

```

- load the device driver.

- # /sbin/insmod pcc

- Make sure if it is successfully loaded.

If you can find, a message "PCC has been installed.", it's OK.

- % /bin/dmesg

# 4.2 General Purpose CAMAC Library

The library is a general purpose CAMAC library. The user interface is common for all CAMAC libraries KEK online group supports [17], [18], [19], [20], [21]. The CAMAC library consists of the following function groups.

- Setup Functions

- CAMAC Functions

- CAMAC Single Actions

- Interrupt Handling

# 4.2.1 Setup Functions

#### camopen

#### • SYNOPSIS

```

#include "camlib.h"

int camopen( int crate );

int CAMOPEN( int crate );

```

#### • DESCRIPTION

camopen opens a CAMAC port to enable access.

#### • RETURN VALUE

On success of **camopen**, zero is returned. If failed, a negative value is returned.

#### camcls

#### • SYNOPSIS

```

#include "camlib.h"

int camcls( int crate );

int CAMCLS( int crate );

```

#### • DESCRIPTION

**camcls** closes the CAMAC port to disable access. **crate** is the number of crate to be opened. For the pipeline CAMAC controller, it is not used.

#### • RETURN VALUE

On success of **camcls**, zero is returned. If failed, a negative value is returned.

#### 4.2.2 CAMAC Functions

#### cgenz

#### • SYNOPSIS

```

#include "camlib.h"

int cgenz( int crate );

int CGENZ( int crate );

```

#### • DESCRIPTION

**cgenz** initializes the CAMAC port. **crate** specifies the crate to be accessed. For the pipeline CAMAC controller, it is not used.

#### • RETURN VALUE

On success of cgenz, zero is returned. If failed, a negative value is returned.

#### cgenc

#### • SYNOPSIS

```

#include "camlib.h"

int cgenc( int crate );

int CGENC( int crate );

```

#### • DESCRIPTION

**cgenc** clears the CAMAC port. **crate** specifies the crate to be accessed. For the pipeline CAMAC controller, it is not used.

#### • RETURN VALUE

On success of **cgenc**, zero is returned. If failed, a negative value is returned.

#### cseti

#### SYNOPSIS

```

#include "camlib.h"

int cseti( int crate );

int CSETI( int crate );

```

#### • DESCRIPTION

**cseti** sets CAMAC INHIBIT on the CAMAC port. **crate** specifies the crate to be accessed. For the pipeline CAMAC controller, it is not used.

#### • RETURN VALUE

On success of **cseti**, zero is returned. If failed, a negative value is returned.

#### cremi

#### SYNOPSIS

```

#include "camlib.h"

int cremi( int crate );

int CREMI( int crate );

```

#### • DESCRIPTION

**cremi** removes CAMAC INHIBIT on the CAMAC crate. **crate** specifies the crate to be accessed. For the pipeline CAMAC controller, it is not used.

#### • RETURN VALUE

On success of **cremi**, zero is returned. If failed, a negative value is returned.

# 4.2.3 CAMAC Single Action

#### camac

#### SYNOPSIS

```

#include "camlib.h"

int camac( int crate, int n, int a, int f, int *data, int *q, int *x );

int CAMAC( int crate, int n, int a, int f, int *data, int *q, int *x );

```

#### • DESCRIPTION

camac accesses CAMAC modules in the CAMAC crate. crate specifies the number of crate to be accessed. For the pipeline CAMAC controller, it is not used. There are CAMAC station number **n**, CAMAC sub-address **a**, CAMAC function **f** and data **data**. After calling the **camac**, the values of CAMAC Q **q** and CAMAC X **x** are returned.

#### • RETURN VALUE

On success of **camac**, zero is returned. If failed, a negative value is returned.

## 4.2.4 Interrupt Handling

#### cenlam

#### • SYNOPSIS

```

#include "camlib.h"

int cenlam( int crate, int mask);

int CENLAM( int crate, int mask);

```

#### DESCRIPTION