# PC/104-Plus Specification

## Version 1.0

February 1997

#### **Please Note**

This specification is subject to change without notice. While every effort has been made to ensure the accuracy of the material contained within this document, the PC/104 Consortium shall under no circumstances be liable for incidental or consequential damages or related expenses resulting from the use of this specification. If errors are found, please notify the PC/104 Consortium.

**PC/104 and PC/104-Plus** are trademarks of the PC/104 Consortium. All other marks are the property of their respective companies.

#### Copyright 1992-97, PC/104 Consortium

Version 1.0 — Page i

## **REVISION HISTORY**

#### Draft 0.7, November 20, 96 - Preliminary Draft

- a. Formatted to meet the requirements of the PC/104 Consortium.

- b. Modify the component restrictions across and to each side of the PC/104 connectors (three sides, .400" from each edge, 4.35" top clearance, .100" bottom clearance).

#### Draft 0.8, December 16, 1996 - Cleanup for release

- a. Correct general typos

- b. Correct word reference error

- c. Add QuickSwitch part number and clarify Mux requirements

- d. Change PCI ONLY to PCI-Only and add note

- e. Correct figure 4 and Figure 5 errors

- f. Correct typo in Table 3

#### Draft 0.9, January 10, 1997 - Cleanup for release

a. Cleanup minor grammatical errors

#### Version 1.0, February 1997 - Initial Release

- a. Grammatical changes and cleanup per review recommendations.

- b. Change Footnote 1 on Page 1 to show future support for the M66EN (66MHz Enable) signal.

- c. Add signals PRSNT[1:2]\* and CLKRUN\* to Figure 1 to encompass all unused PCI signals.

- d. Moved the Mechanical section after the Electrical section.

- e. Clarified the KEY pin usage for universal modules and defined them as ground connections.

- f. Clarified pin 1 for the PC/104-*Plus* connectors on Figure 4.

- g. Added an example manufacturer and part No. for the PCI connector (Figure 5) and Shroud (Figure 6).

- h. Modified Figure 2, Table 1, and some text under Section 2.2 to add routing recommendations for the PCI interrupt lines INTA INTD.

## TABLE OF CONTENTS

| 1. INTRODUCTION1                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 SUMMARY OF KEY DIFFERENCES FROM PC/104 SPECIFICATION: 1   1.2 SUMMARY OF KEY DIFFERENCES (120-PIN PCI AND PCI LOCAL BUS SPECIFICATION) 1   1.3 REFERENCES 1                                  |

| 2. PCI SIGNAL DEFINITION                                                                                                                                                                         |

| 2.1 PCI BUS SIGNAL DESCRIPTION12.1.1 System12.1.2 Address and Data12.1.3 Interface Control Pins12.1.4 Arbitration (Bus Masters Only)12.1.5 Error Reporting12.1.6 Interrupts12.2 SIGNAL GROUPING1 |

| 3. ELECTRICAL SPECIFICATION1                                                                                                                                                                     |

| 3.1 PC/104 Bus13.2 PCI Bus13.2.1 Signal Definitions13.2.2 Signal Assignments13.2.3 Power And Ground Pins13.2.4 Key Locations13.2.5 AC/DC Signal Specifications13.3 MODULE POWER REQUIREMENTS1    |

| 4. LEVELS OF CONFORMANCE1                                                                                                                                                                        |

| 4.1 PC/104-Plus "Compliant" 1   4.2 PC/104-Plus "Bus-compatible" 1   4.3 PC/104-Plus "PCI-ONLY" 1                                                                                                |

| 5. MECHANICAL SPECIFICATION1                                                                                                                                                                     |

| 5.1 MODULE DIMENSIONS. 1   5.2 CONNECTOR AND SHROUD 1                                                                                                                                            |

| 6. TYPICAL MODULE STACK1                                                                                                                                                                         |

#### APPENDICES

| A. MECHANICAL DIMENSIONS  | A- | 1 |

|---------------------------|----|---|

| B. BUS SIGNAL ASSIGNMENTS | B- | 1 |

Version 1.0 — Page iv

## **TABLE OF FIGURES**

| FIGURE 1: PCI PIN LIST1        |

|--------------------------------|

| FIGURE 2: SIGNAL SELECT        |

| FIGURE 3: TYPICAL MODULE STACK |

| FIGURE 4: MODULE DIMENSIONS    |

| FIGURE 5: PCI CONNECTOR        |

| FIGURE 6: PCI SHROUD1          |

## TABLE OF TABLES

| FIGURE 1: PCI PIN LIST         |

|--------------------------------|

| FIGURE 2: SIGNAL SELECT        |

| FIGURE 3: TYPICAL MODULE STACK |

| FIGURE 4: MODULE DIMENSIONS    |

| FIGURE 5: PCI CONNECTOR        |

| FIGURE 6: PCI SHROUD           |

#### PC/104-Plus SPECIFICATION Version 1.0 February 1997

#### 1. INTRODUCTION

While the PC/AT architecture is becoming increasingly popular in embedded applications, there is an increasing need for a higher performance Bus throughput. This is especially true when it comes to graphics devices as well as other high speed I/O devices such as networks.

This document supplies the mechanical and electrical specifications for the "PC/104-*Plus*" and incorporates all of the PC/104 features, with the added advantage of the high speed PCI bus. The physical size, mounting configuration and electrical interconnect portion of the PC/104 specification shall remain unchanged.

#### 1.1 Summary of Key Differences From PC/104 Specification:

- A third connector opposite the PC/104 connectors supports the PCI bus.

- Changes to the component height requirements increase the flexibility of the module.

- Control logic added to handle the requirements for the high speed bus.

#### 1.2 Summary of Key Differences (120-pin PCI and PCI Local Bus Specification)

- The PCI bus connector is a 4x30 (120-pin) 2mm pitch stackthrough connector as opposed to the 124-pin edge connector on standard 32-bit PCI Local Bus.

- The 120-pin PCI does not support 64-bit Extensions, JTAG, PRSNT, or CLKRUN signals.

#### **1.3 References**

This document covers the addition of the PCI functions. The following documents should be used as reference for a detailed understanding of the overall system requirements:

- PC/104 Specification Version 2.3

- PCI Local Bus Specification Revision 2.1

Contact the PCI Special Interest Group office for the latest revision of the PCI specification:

#### PCI Special Interest Group P.O. Box 14070 Portland, OR 97214 800.433.5177 (U.S.) 503.797.4207 (International)

If errors are found in this document, please send a written copy of the suggested corrections to:

#### PC/104 Consortium

849B Independence Ave Mountain View, CA 94043

Version 1.0 — Page 1

Tel 415.903.8304 Fax 415.967.0995

#### 2. PCI SIGNAL DEFINITION

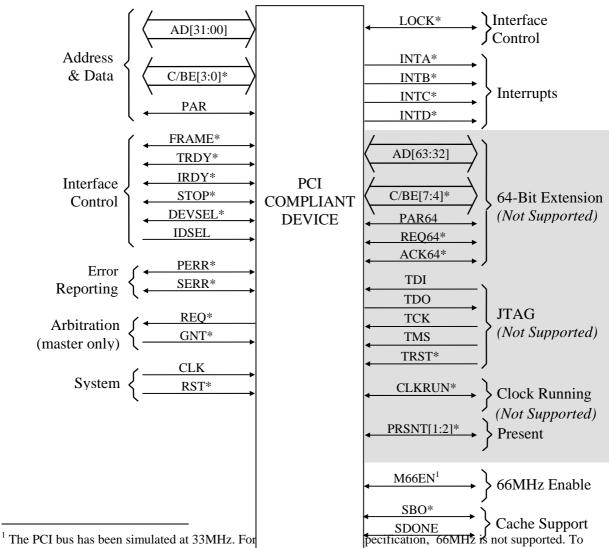

Figure 1 shows the pins in functional groups, with the required pins on the left and the optional pins on the right side. The shaded pins on the right are unsupported features, but are included to show the entire PCI bus as defined in the PCI Revision 2.1 Specification. This version of the PCI bus is intended as a 32-bit bus running at 33MHz and therefore, 64-bit extension and 66MHz<sup>1</sup> are not supported at this time. Also not supported are the boundary scan features (JTAG), *Present* (PRSNR[1:2]\*), and *Clock running* (CLKRUN\*). The direction indication on the pins assumes a combination master/target device.

Figure 1: PCI Pin List

support future enhancements, the M66EN signal should be grounded on any module that cannot support 66MHz and left open for modules that can support a 66MHz clocks.

#### 2.1 PCI Bus Signal Description

#### 2.1.1 System

| CLK  | <b>Clock</b> provides timing for all transactions on the PCI bus.      |

|------|------------------------------------------------------------------------|

| RST* | <b>Reset</b> is used to bring PCI-specific registers to a known state. |

#### 2.1.2 Address and Data

| AD[31:00]  | Address and Data are multiplexed. A bus transaction consists of an address cycle followed by one or more data cycles.                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| C/BE[3:0]* | <b>Bus Command/Byte Enables</b> are multiplexed. During the address cycle, the command is defined. During the Data cycle, they define the byte enables. |

PAR **Parity** is even on AD[31:00] and C/BE[3:0]\* and is required.

#### 2.1.3 Interface Control Pins

| FRAME*  | <b>Frame</b> is driven by the current master to indicate the start of a transaction and will remain active until the final data cycle.                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRDY*   | <b>Initiator Ready</b> indicates the master's ability to complete the current data cycle of the transaction.                                                                       |

| TRDY*   | <b>Target Ready</b> indicates the selected devices ability to complete the current data cycle of the transaction. Both IRDY* and TRDY* must be asserted to terminate a data cycle. |

| STOP*   | <b>Stop</b> indicates the current selected device is requesting the master to stop the current transaction.                                                                        |

| LOCK*   | <b>Lock</b> indicates an operation that may require multiple transactions to complete.                                                                                             |

| IDSEL   | Initialization Device Select is used as a chip-select during configuration.                                                                                                        |

| DEVSEL* | <b>Device Select</b> is driven by the target device when its address is decoded.                                                                                                   |

#### 2.1.4 Arbitration (Bus Masters Only)

| REQ* | <b>Request</b> indicates to the arbitrator that this device desires use of the bus. |

|------|-------------------------------------------------------------------------------------|

| GNT* | Grant indicates to the requesting device that access has been granted.              |

#### 2.1.5 Error Reporting

| PERR* | Parity Error is for reporting data parity errors.    |

|-------|------------------------------------------------------|

| SERR* | System Error is for reporting address parity errors. |

#### 2.1.6 Interrupts

| INTA* | <b>Interrupt A</b> is used to request an Interrupt.                               |

|-------|-----------------------------------------------------------------------------------|

| INTB* | <b>Interrupt B</b> is used to request interrupts only for multi-function devices. |

| INTC* | Interrupts C is used to request interrupts only for multi-function devices.       |

INTD\* Interrupts D is used to request interrupts only for multi-function devices.

#### 2.2 Signal Grouping

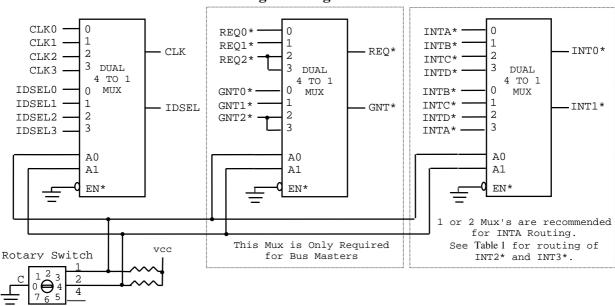

A means of selecting the appropriate signals must be established that will easily allow for the installation and configuration of add-in PC/104-*Plus* modules. Figure 2 shows such a method:

**Figure 2: Signal Select**

The multiplexer chips are Dual 4:1 Mux/Demux chips (QuickSwitch® QS3253 or equivalent). They provide a 5 $\Omega$  switch that connects the input and output together. The nature of the switches, provide a bi-directional path with no signal propagation delay other than the RC delay of the on resistance of the switch and the load capacitance. This is typically 250ps at 50pF Load.

Other methods of configuring the modules are possible, but the rotary switch is the most convenient, cleanest and provides for the least possible error in configuration.

The clocks are tuned on the Host Board such that the length of CLK3 trace is  $\approx 0.662$ " less than CLK2, CLK2 trace is  $\approx 0.662$ " less than CLK1, and CLK1 trace is  $\approx 0.662$ " less than CLK0. Therefore, the first module on the stack must select CLK0 (the longest trace), the second CLK1, etc. This provides basically no clock skew between modules. Table 1 shows the appropriate switch setting and signals used for each module in the stack. It is recommended that additional Mux chips be added to route Interrupts if required. Use one Mux for 1 to 2 interrupts or two Mux's for 3 to 4 interrupts.

| Table 1: | Rotary | Switch | Settings |

|----------|--------|--------|----------|

|----------|--------|--------|----------|

| Switch | Module | REQ* | GNT* | CLK | IDSEL | ID | INT0* | INT1* | INT2* | INT3* |

|--------|--------|------|------|-----|-------|----|-------|-------|-------|-------|

| Position | Slot |        |                    |      |        | Address |       |       |       |       |

|----------|------|--------|--------------------|------|--------|---------|-------|-------|-------|-------|

| 0 or 4   | 1    | REQ0*  | GNT0*              | CLK0 | IDSEL0 | AD20    | INTA* | INTD* | INTC* | INTB* |

| 1 or 5   | 2    | REQ1*  | GNT1*              | CLK1 | IDSEL1 | AD21    | INTB* | INTA* | INTD* | INTC* |

| 2 or 6   | 3    | REQ2*1 | GNT2* <sup>1</sup> | CLK2 | IDSEL2 | AD22    | INTC* | INTB* | INTA* | INTD* |

| 3 or 7   | 4    | REQ2*1 | GNT2*1             | CLK3 | IDSEL3 | AD23    | INTD* | INTC* | INTB* | INTA* |

Note 1: Because module slots 3 and 4 share REQ2/GNT2, they cannot both be bus master devices.

#### 3. ELECTRICAL SPECIFICATION

#### 3.1 PC/104 Bus

The electrical specifications for the PC/104 bus for bus drive current, bus termination, pullup/pulldown resistors, etc. are unchanged and are defined in the PC/104 Specification. The signal assignments for the J1/P1 and J2/P2 connector are given in Appendix B, Table 4: PC/104 Bus (Reference Only).

#### 3.2 PCI Bus

The PCI Bus mechanical interface is a stackable 30x4 header. This interface carries all of the required PCI signals per *PCI Local Bus Specification Version. 2.1*.

#### 3.2.1 Signal Definitions

For full details on the electrical requirements for the PCI bus, reference the *PCI Local Bus Specification Version. 2.1.*

#### 3.2.2 Signal Assignments

Signals are assigned in the same relative order as in the PCI Local Bus Specification, but transformed to the corresponding header connector pins. Because of the stackthrough nature of the bus, slot-specific signals are duplicated for each plug-in module. The system has been designed to accommodate 4 PC/104-*Plus* modules, so multiple sets of the signals have been duplicated to accommodate one signal for each module. These four signal groups include: IDSEL[3:0] - CLK[3:0] - REQ\*[2:0] - GNT\*[2:0]. Signal assignments for the J3/P3 connector are given in Appendix B, Table 3: PC/104-Plus Bus Signal Assignments.

#### 3.2.3 Power And Ground Pins

The total number of power and ground signals remains the same, but the +3.3 V pins have been reduced by two and the ground pins have been increased by two. The change was the result of signal grouping on the bus and has no effect on performance or integrity.

#### 3.2.4 Key Locations

The KEY pins are to guarantee proper module installation. Pin-A1 will be removed and the female side plugged for 5.0V I/O signals and Pin-D30 will be modified in the same manner

for 3.3V I/O. Universal boards which can support either signal levels will have both key pins implemented. Universal boards must therefore be located at the top of the stack. See Appendix B, Table 3: PC/104-Plus Bus Signal Assignments.

#### 3.2.5 AC/DC Signal Specifications

All bus timing and signal levels are identical to the *PCI Local Bus Specification Revision* 2.1.

#### 3.3 Module Power Requirements

Table 2 specifies the voltage and maximum power requirements for each PC/104-*Plus* module. It should be noted that although the maximum requirements as specified are the same as the standard PC/104 specification, care should be used in designing PC/104-*Plus* modules to guarantee the least possible power consumption. A worst case module as specified could use almost 39 Watts of power, which would basically be unacceptable in most systems.

| Supply      | Min. Voltage | Max. Voltage | Max. Current | Max. Power |

|-------------|--------------|--------------|--------------|------------|

| $+3.3V^{1}$ | 3.00         | 3.60         | 3A           | 10.8W      |

| +5V         | 4.75         | 5.25         | 2A           | 10.5W      |

| +12V        | 11.4         | 12.6         | 1A           | 12.6W      |

| -5V         | -5.25        | -4.75        | 0.2A         | 1.05W      |

| -12V        | -12.6        | -11.4        | 0.3A         | 3.78W      |

**Table 2: Module Power Requirements**

Note 1: Host Boards implementing 5V signaling are not required to supply 3.3 volts to the modules, but must provide a bus and decoupling. If 3.3 volts is required for a module using the 5V signaling method, provisions should be made to provide its own 3.3 volts by means of an onboard regulator or some other input source. Host Boards implementing 3.3V signaling are required to supply 3.3 volts to the modules.

#### 4. LEVELS OF CONFORMANCE

This section provides terminology intended to assist manufacturers and users of PC/104-*Plus* bus-compatible products in defining and specifying conformance with the PC/104-*Plus* Specification.

#### 4.1 PC/104-Plus "Compliant"

This refers to "PC/104-*Plus* form-factor" devices that conform to all non-optional aspects of the PC/104-*Plus* Specification, including both *mechanical* and *electrical* specifications.

#### 4.2 PC/104-Plus "Bus-compatible"

This refers to devices which are not "PC/104-*Plus* form-factor" (i.e., do not comply with the module dimensions of the PC/104-*Plus* Specification), but provide male or female PC/104-*Plus* bus connectors that meets both the *mechanical* and *electrical* specifications provided for the PC/104-*Plus* bus connectors.

#### 4.3 PC/104-Plus "PCI-Only"<sup>2</sup>

Because the PC/104-*Plus* standard encompasses two different buses (i.e. PC/104 104-pin "ISA" bus and 120-pin "PCI" bus), it is possible for PC/104-*Plus* compliant or compatible modules to

<sup>&</sup>lt;sup>2</sup> This precludes stacking standard PC/104 Modules.

implement PCI only. Such modules shall have the added designation "PCI-Only" in addition to the designation specified in either 4.1 and 4.2. Example: PC/104-*Plus* "Compliant", PCI-Only or PC/104-*Plus* "Bus-compatible", PCI-Only.

### 5. MECHANICAL SPECIFICATION

#### 5.1 Module Dimensions

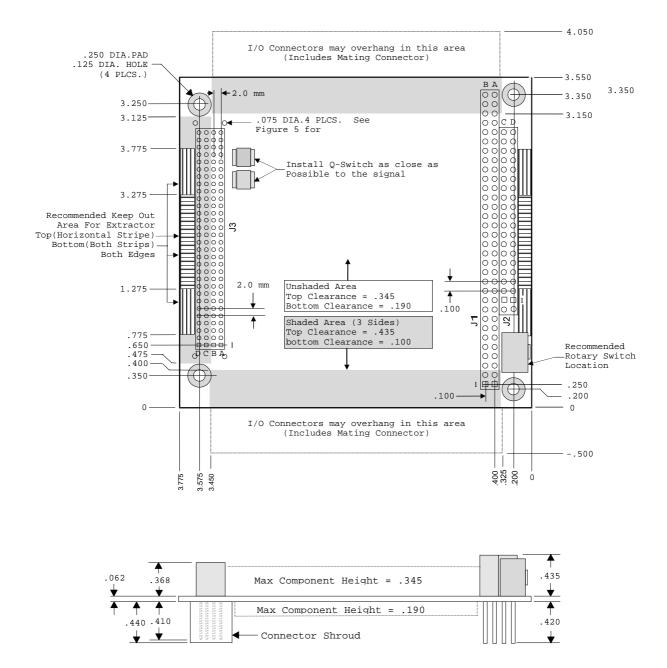

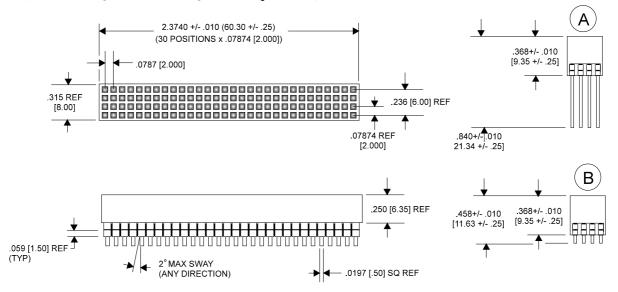

The mechanical dimensions for this module are identical to PC/104 specification with the exception of the added connector (J3), some modifications to the I/O connector area, and changes to the component height restrictions. The component height on the top side has been reduced from 0.435" to 0.345" and the bottom has been increased from 0.100" to 0.190". The component restrictions across and to each side of the PC/104 connectors (three sides, 0.400" from each edge) remains the same as the PC/104 specification. The mechanical dimensions and restrictions are given in Appendix A, Figure 4: Module Dimensions.

#### 5.2 Connector And Shroud

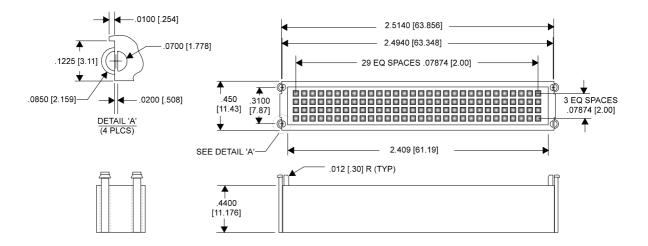

The PC/104-*Plus* connector for the PCI bus is a 4x30 (120-pin) 2mm pitch connector. The Shroud should be installed on the bottom of the PC board when a stackthrough connector is used. The mechanical dimensions and restrictions are given in Appendix A, Figure 5: PCI Connector.

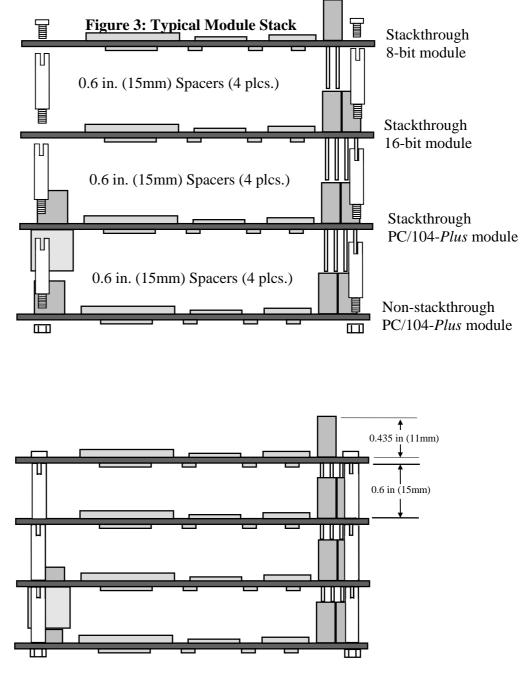

#### 6. TYPICAL MODULE STACK

Figure 3 shows a typical module stack with 2 PC/104-*Plus* modules, 1 PC/104 16-Bit module, and 1 PC/104 8-Bit module. The maximum configuration for the PCI bus of PC/104-*Plus* modules is 4 plus the Host Board. If standard PC/104 modules are used in the stack, they must be the top module(s) because they will normally not include the PCI bus.

Version 1.0 — Page 10

## APPENDIX A

## MECHANICAL DIMENSIONS

Version 1.0 — Page A-1

#### PC/104-Plus

#### **Figure 4: Module Dimensions**

#### Version 1.0 — Page A-2

#### PC/104-Plus

#### **Figure 5: PCI Connector**

- (A) shows the pin dimensions for the Stackthrough connector. (Samtec ESQT-130-02-G-Q-368 or equivalent)

- (B) shows the pin dimensions for the Soldertail connector. (Samtec ESQT-130-03-M-Q-368 or equivalent)

**Figure 6: PCI Shroud**

(Samtec TS-30-Q or equivalent)

## APPENDIX B

## BUS SIGNAL ASSIGNMENTS

Version 1.0 — Page B-1

| J3/P3 |                           |          |          |                           |  |  |

|-------|---------------------------|----------|----------|---------------------------|--|--|

| Pin   | Α                         | В        | С        | D                         |  |  |

| 1     | GND/5.0V KEY <sup>2</sup> | Reserved | +5       | AD00                      |  |  |

| 2     | VI/O                      | AD02     | AD01     | +5V                       |  |  |

| 3     | AD05                      | GND      | AD04     | AD03                      |  |  |

| 4     | C/BE0*                    | AD07     | GND      | AD06                      |  |  |

| 5     | GND                       | AD09     | AD08     | GND                       |  |  |

| 6     | AD11                      | VI/O     | AD10     | M66EN                     |  |  |

| 7     | AD14                      | AD13     | GND      | AD12                      |  |  |

| 8     | +3.3V                     | C/BE1*   | AD15     | +3.3V                     |  |  |

| 9     | SERR*                     | GND      | SB0*     | PAR                       |  |  |

| 10    | GND                       | PERR*    | +3.3V    | SDONE                     |  |  |

| 11    | STOP*                     | +3.3V    | LOCK*    | GND                       |  |  |

| 12    | +3.3V                     | TRDY*    | GND      | DEVSEL*                   |  |  |

| 13    | FRAME*                    | GND      | IRDY*    | +3.3V                     |  |  |

| 14    | GND                       | AD16     | +3.3V    | C/BE2*                    |  |  |

| 15    | AD18                      | +3.3V    | AD17     | GND                       |  |  |

| 16    | AD21                      | AD20     | GND      | AD19                      |  |  |

| 17    | +3.3V                     | AD23     | AD22     | +3.3V                     |  |  |

| 18    | IDSEL0                    | GND      | IDSEL1   | IDSEL2                    |  |  |

| 19    | AD24                      | C/BE3*   | VI/O     | IDSEL3                    |  |  |

| 20    | GND                       | AD26     | AD25     | GND                       |  |  |

| 21    | AD29                      | +5V      | AD28     | AD27                      |  |  |

| 22    | +5V                       | AD30     | GND      | AD31                      |  |  |

| 23    | REQ0*                     | GND      | REQ1*    | VI/O                      |  |  |

| 24    | GND                       | REQ2*    | +5V      | GNT0*                     |  |  |

| 25    | GNT1*                     | VI/O     | GNT2*    | GND                       |  |  |

| 26    | +5V                       | CLK0     | GND      | CLK1                      |  |  |

| 27    | CLK2                      | +5V      | CLK3     | GND                       |  |  |

| 28    | GND                       | INTD*    | +5V      | RST*                      |  |  |

| 29    | +12V                      | INTA*    | INTB*    | INTC*                     |  |  |

| 30    | -12V                      | Reserved | Reserved | GND/3.3V KEY <sup>2</sup> |  |  |

| Table 3: PC/104-Plus | Bus Signal Assignments |

|----------------------|------------------------|

|----------------------|------------------------|

Notes: 1. The shaded area denotes power or ground signals.

2. The KEY pins are to guarantee proper module installation. Pin-A1 will be removed and the female side plugged for 5.0V I/O signals and Pin-D30 will be modified in the same manner for 3.3V I/O. It is recommended that both KEY pins (A1 and D30) be electrically connected to GND for shielding.

|       |          |         | J1/P1 |         |                 |  |

|-------|----------|---------|-------|---------|-----------------|--|

|       |          |         |       | Α       | В               |  |

|       |          |         | 1     | IOCHCK* | GND             |  |

|       |          |         | 2     | D7      | RSTDRV          |  |

| Ī     |          |         | 3     | D6      | +5V             |  |

|       |          |         | 4     | D5      | IRQ9            |  |

|       |          |         | 5     | D4      | -5V             |  |

|       |          |         | 6     | D3      | DRQ2            |  |

| J2/P2 |          |         | 7     | D2      | -12V            |  |

| Pin   | D        | С       | 8     | D1      | ENDXFR*         |  |

| 0     | GND      | GND     | 9     | D0      | +12V            |  |

| 1     | MEMCS16* | SBHE*   | 10    | IOCHRDY | GND/KEY         |  |

| 2     | IOCS16*  | LA23    | 11    | AEN     | SMEMW*          |  |

| 3     | IRQ10    | LA22    | 12    | A19     | SMEMR*          |  |

| 4     | IRQ11    | LS21    | 13    | A18     | IOW*            |  |

| 5     | IRQ12    | LS20    | 14    | A17     | IOR*            |  |

| 6     | IRQ15    | LS19    | 15    | A16     | DACK3*          |  |

| 7     | IRQ14    | LA18    | 16    | A15     | DRQ3            |  |

| 8     | DACK0*   | LA17    | 17    | A14     | DACK1*          |  |

| 9     | DRQ0     | MEMR*   | 18    | A13     | DRQ1            |  |

| 10    | DACK5*   | MEMW*   | 19    | A12     | <b>REFRESH*</b> |  |

| 11    | DRQ5     | SD8     | 20    | A11     | SYSCLK          |  |

| 12    | DACK6*   | SD9     | 21    | A10     | IRQ7            |  |

| 13    | DRQ6     | SD10    | 22    | A9      | IRQ6            |  |

| 14    | DACK7*   | SD11    | 23    | A8      | IRQ5            |  |

| 15    | DRQ7     | SD12    | 24    | A7      | IRQ4            |  |

| 16    | +5V      | SD13    | 25    | A6      | IRQ3            |  |

| 17    | MASTER*  | SD14    | 26    | A5      | DACK2*          |  |

| 18    | GND      | SD15    | 27    | A4      | TC              |  |

| 19    | GND      | GND/KEY | 28    | A3      | BALE            |  |

|       |          |         | 29    | A2      | +5V             |  |

|       |          |         | 30    | A1      | OSC             |  |

|       |          |         | 31    | A0      | GND             |  |

|       |          |         | 32    | GND     | GND             |  |