# IEEE Standard for Heterogeneous InterConnect (HIC) (Low-Cost, Low-Latency Scalable Serial Interconnect for Parallel System Construction)

Sponsor Bus Architecture Standards Committee of the IEEE Computer Society

Approved 21 September 1995

**IEEE Standards Board**

**Abstract:** Enabling the construction of high-performance, scalable, modular, parallel systems with low system integration cost is discussed. Complementary use of physical connectors and cables, electrical properties, and logical protocols for point-to-point serial scalable interconnect, operating at speeds of 10–200 Mb/s and at 1 Gb/s in copper and optic technologies, is described.

**Keywords:** flow control, encoding schemes, OMI/HIC, packet routing, parallelism, point-to-point serial scalable interconnect, protocols, routing fabric, serial links, serialization, silicon integration, switch chip, transaction layer, wormhole routing

ISBN 1-55937-595-7

The Institute of Electrical and Electronics Engineers, Inc.

<sup>345</sup> East 47th Street, New York, NY 10017-2394, USA

Copyright © 1996 by the Institute of Electrical and Electronics Engineer, Inc.

All rights reserved. Published 1996. Printed in the United States of America.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

**IEEE Standards** documents are developed within the Technical Committees of the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members of the committees serve voluntarily and without compensation. They are not necessarily members of the Institute. The standards developed within IEEE represent a consensus of the broad expertise on the subject within the Institute as well as those activities outside of IEEE that have expressed an interest in participating in the development of the standard.

Use of an IEEE Standard is wholly voluntary. The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a document is more than five years old and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of all concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason IEEE and the members of its technical committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 USA

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying all patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

Authorization to photocopy portions of any individual standard for internal or personal use is granted by the Institute of Electrical and Electronics Engineers, Inc., provided that the appropriate fee is paid to Copyright Clearance Center. To arrange for payment of licensing fee, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; (508) 750-8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

# Introduction

[This introduction is not part of IEEE Std 1355-1995, IEEE Standard for Heterogeneous InterConnect (HIC) (Low-Cost, Low-Latency Scalable Serial Interconnect for Parallel System Construction).]

The construction of high-performance systems with parallel communications, parallel processing, and/or parallel I/O demands a fast, low-cost, low-latency interconnect. It must be fast and low-latency, otherwise it will be the limiting factor in system performance; and it must be low-cost, or it will dominate the system cost. It must also scale well in both performance and cost relative to the system size, otherwise highly parallel systems will be limited in performance or too expensive. Existing standards do not meet these criteria, because they are designed for communication over long distances (which incurs high costs), or because they aim at the extreme of currently achievable performance (which again increases costs), or because they are based on a restricted model such as a bus, which limits overall performance and scalability. A detailed rationale for this standard is given in annex D.

This standard has been developed to complement recent technical developments of highly integrated, low power interconnect technology implemented in high volume commodity VLSI processes, and to exploit the simplifications in encodings and protocols resulting from the use of relatively reliable media over relatively short distances. Aspects of the baseline for this standard have their origins in work on parallel systems, which has taken place in a number of ESPRIT projects. In particular, the routing strategy was established in the PUMA project, and the DS-Links were developed partially in the GP MIMD project. Work at interconnect for high performance mainframe computers at Bull led to the development of the gigabit link technology implemented in Bi-CMOS and CMOS processes. More recently, these developments, together with corresponding optical technology, have been brought together in the OMI/HIC Project (Open Microprocessor Systems Initiative—High Performance Heterogeneous Interconnect—ESPRIT 7252).

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying all patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

The patent holder has, however, filed a statement of assurance that it will grant a license under these rights without compensation or under reasonable rates and nondiscriminatory, reasonable terms and conditions to all applicants desiring to obtain such a license. The IEEE makes no representation as to the reasonableness of rates and/or terms and conditions of the license agreement offered by the patent holder. Contact information may be obtained from the IEEE Standards Department.

This standard has been developed with the efforts of many volunteers. The following is a list of those who attended Working Group meetings while the draft and final standard documents were compiled:

## Colin Whitby-Strevens, Chair Roland Marbot, (Co-Chair) Andrew Coffer, Editor

Harry Andreas Noriaki Arikawa Dan Ater Ton Balhaar Edmund H. Baulsir Harrison Beasley Ralf Bokämper Thierry Brizard Joe Brown Richard Carlson Stephen J. Cecil Jean Jacques Chaput Michael Christ Chip Coffin Stefan De Troch Jean-Merri De Vanssay Gerry Desmody Ian Dobson Jean Jacques Dumont Mike Foster David Franklin Bob Gannon Stein Gjessing Oystein Gran Larsen Howard Gurney Claes-Göran Gustavsson Stefan Haas Brian Henderson Geoffrey Hilton Roger Hinsdale Geir Horn Shinichi Iwano Ed Jacques

| Bjørn Johnsbråten   | Kristian Martinson |

|---------------------|--------------------|

| Anatol Kaganovich   | Paolo Melloni      |

| Thomas Kessler      | Michel Monchant    |

| Jangkyung Kim       | Jonathan Morris    |

| Terry Kingham       | Ken Naumann        |

| Bill Kirk           | Joe Norris         |

| Matthew Kirwan      | Mats Olstedt       |

| Ernst Kristiansen   | Joar Martin Østby  |

| Alain Lagarde       | Sylvain Paineau    |

| Falk Langhammer     | Elwood Parsons     |

| Craig Lund          | David Robak        |

| Calogero Mantellina | Eivind Rongved     |

| Brian Martin        | Pino Rosario       |

Contributions have also been received from:

| Yogindra Abhyankar | Bruno Houssay   | James Wolffe |

|--------------------|-----------------|--------------|

| Dave Cormie        | Reza Nezamzadeh | Bin Wu       |

The following persons were on the balloting committee:

| Ghassan Abbas         | Stein Gj  |

|-----------------------|-----------|

| Malcom Airst          | Chuck C   |

| Harry Andreas         | Peter Gu  |

| Keith Anthony         | Stefan H  |

| James Barnette        | Bruno H   |

| Edmund Baulsir        | Phillip I |

| Harrison Beasley      | Shinichi  |

| Christos Bezirtzoglou | David Ja  |

| Harold Blatter        | Daniel J  |

| Timothy Boggess       | Sherry J  |

| Ralf Bokämper         | Sun-Mo    |

| John Brightwell       | Yoshihi   |

| Charles Brill         | Stephen   |

| Chris Brown           | Jangkyu   |

| Joe Brown             | Jan Kin   |

| Trevor Carden         | Hans Pe   |

| Richard Carlson       | Ernst K   |

| Yoon Chang            | Thomas    |

| Andy Cheese           | Falk La   |

| C. Chen               | Conrad    |

| Michael Christ        | Michael   |

| Andrew Coffer         | Udo Leo   |

| Patrick Courtney      | Rollins   |

| Robert Crowder        | Gary M    |

| Robert Dahlgren       | Roland    |

| Martin Davis          | Joseph I  |

| Dante Del Corso       | Brian M   |

| Ian Dobson            | Wolfgar   |

| Jean-Jacques Dumont   | Michel    |

| Sourav Dutta          | Michael   |

| Wayne Fischer         | Yoshiki   |

| Gordon Force          | Klaus-D   |

| Bob Gannon            | Michael   |

|                       |           |

jessing Grant utgarts Haas Houssay Hughes i Iwano ames Jochym Johnson oo Kang sa Kawamura n Kempainen unk Kim ndervater eter Kraus ristiansen s Kulesza nghammer Laurvick l Lazar chner Linser lanchester Marbot Marshall **A**artin ing Meier Maillet el Miskin Mitani Dieter Mueller l Munroe

Jouko Saarinen Yasuo Sasaki Michael Scottp Tor Skeie Nobuaki Sugiura Peter Thompson Joe Trainor Toine van Laarhoven Rob Volgersp Richard Wagner Paul Walker Alan Welzel David L. Wright

J. Nicoud Joe Norris Daniel O'Connor Katsuyuki Okada Fred Orlando Granville Ott Elwood Parsons Mohan Patnaik Lalit Mira Pauker Patrick Plancke Mike Polehn Brian Ramelson Douglas Rawson-Harris David Robak Fred Rosenberger Yasuo Sasaki Frederick Sauer Rudolf Schubert Shreyas Shah Tahir Sheikh Tor Skeie Paul Slootweg Nobuaki Sugiura Michael Teener Michael Thompson Peter Thompson Michael Timperman Dirk Van de Lagemaat Richard Wagner Paul Walker Thomas Wegmann Alan Wetzel Colin Whitby-Strevens

Jeffrey Wills James Wolffe Anthony Wood J. Robert Wood Bill Woodruff David Wright Bin Wu Oren Yuen Janusz Zalewski

When the IEEE Standards Board approved this standard on September 21, 1995, it had the following membership:

# E.G. "Al" Kiener, Chair Donald C. Loughry, Vice Chair Andrew G. Salem, Secretary

| Gilles A. Baril        | Jim Isaak              | Mary Lou Padgett  |

|------------------------|------------------------|-------------------|

| Clyde R. Camp          | Ben C. Johnson         | John W. Pope      |

| Joseph A. Cannatelli   | Sonny Kasturi          | Arthur K. Reilly  |

| Stephen L. Diamond     | Lorraine C. Kevra      | Gary S. Robinson  |

| Harold E. Epstein      | Ivor N. Knight         | Ingo Rüsch        |

| Donald C. Fleckenstein | Joseph L. Koepfinger*  | Chee Kiow Tan     |

| Jay Forster*           | D. N. "Jim" Logothetis | Leonard L. Tripp  |

| Donald N. Heirman      | L. Bruce McClung       | Howard L. Wolfman |

| Richard J. Holleman    | Marco W. Migliaro      |                   |

\*Member Emeritus

Also included are the following nonvoting IEEE Standards Board liaisons:

Satish K. Aggarwal Richard B. Engelman Robert E. Hebner Chester C. Taylor

Lisa S. Young IEEE Standards Project Editor

| CLA | USE                                                                                              | PAGE |

|-----|--------------------------------------------------------------------------------------------------|------|

| 1.  | Overview                                                                                         | 1    |

|     | 1.1 Scope                                                                                        |      |

|     | 1.2 Purpose                                                                                      |      |

| 2.  | References                                                                                       | 1    |

| 3.  | Definitions                                                                                      | 3    |

| 5.  |                                                                                                  |      |

|     | <ul><li>3.1 General</li><li>3.2 Glossary</li></ul>                                               |      |

|     |                                                                                                  |      |

| 4.  | Physical media and logical layers                                                                | 6    |

|     | 4.1 Physical media                                                                               |      |

|     | <ul><li>4.2 Logical layers</li><li>4.3 Interaction of layers</li></ul>                           |      |

|     | <ul><li>4.3 Implementations defined in the standard</li></ul>                                    |      |

| 5.  | DS-SE and DS-DE                                                                                  | 14   |

| 5.  |                                                                                                  |      |

|     | 5.1 General                                                                                      |      |

|     | <ul><li>5.2 DS-SE: physical medium</li><li>5.3 DS-SE signal level</li></ul>                      |      |

|     | •                                                                                                |      |

|     |                                                                                                  |      |

|     | 5.5 DS-DE signal level                                                                           |      |

|     | <ul><li>5.6 DS-SE and DS-DE character level</li><li>5.7 DS-SE and DS-DE exchange level</li></ul> |      |

| 6.  | TS-FO-02 fiber optic link                                                                        |      |

|     | 6.1 Physical medium                                                                              | 32   |

|     | 6.2 Signal level                                                                                 |      |

|     | 6.3 TS-FO character level                                                                        |      |

|     | 6.4 TS-FO exchange level                                                                         |      |

| 7.  | HS-SE-10                                                                                         | 41   |

|     | 7.1 HS-SE physical medium                                                                        |      |

|     | 7.2 HS-SE signal level                                                                           |      |

|     | 7.3 HS character level (8B/12B code)                                                             |      |

|     | 7.4 HS exchange level                                                                            |      |

| 8.  | HS-FO-10 fiber optic link                                                                        |      |

|     | 8.1 Physical medium                                                                              |      |

|     | 8.2 Signal level                                                                                 |      |

|     | 8.3 Character level end exchange level                                                           |      |

| 9.  | Common packet level                                                                              |      |

|     | 9.1 General discussion                                                                           |      |

|     | 9.2 Packet format                                                                                |      |

|     |                                                                                                  |      |

#

| CLAU  | SE                                                                                                                                          | PAGE |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------|------|

|       | <ul><li>9.3 Networks and routing</li><li>9.4 Error detection, recovery, and reporting</li></ul>                                             |      |

| 10.   | Conformance criteria                                                                                                                        | 79   |

|       | <ul> <li>10.1 Conformance statements</li> <li>10.2 Definition of subsets</li> <li>10.3 Conformance statements and cable markings</li> </ul> | 79   |

| Annex | A (Normative) DS-DE connector specification                                                                                                 | 81   |

| Annex | B (Normative) HS-SE connector specification                                                                                                 | 88   |

| Annex | C (Normative) TS-FO and HS-FO connector specifications                                                                                      | 93   |

| Annex | D (Informative) Rationale                                                                                                                   | 107  |

| Annex | E (Informative) Switch chips, switches, and fabrics                                                                                         | 111  |

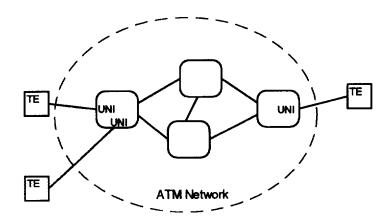

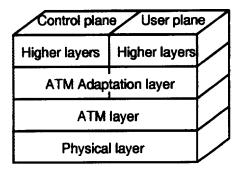

| Annex | F (Informative) Use of the transaction layer—Asynchronous transfer mode (ATM) example                                                       | 112  |

| Annex | G (Informative) Error handling                                                                                                              | 121  |

| Annex | H (Informative) Flow control calculations                                                                                                   | 122  |

| Annex | I (Informative) Synchronized channel communications                                                                                         | 124  |

| Annex | J (Informative) Example DS-SE driver circuit                                                                                                | 127  |

| Annex | K (Informative) DS-DE optional power supply recommendation                                                                                  | 129  |

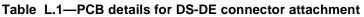

| Annex | L (Informative) DS-DE fixed connector PCB recommendation                                                                                    | 130  |

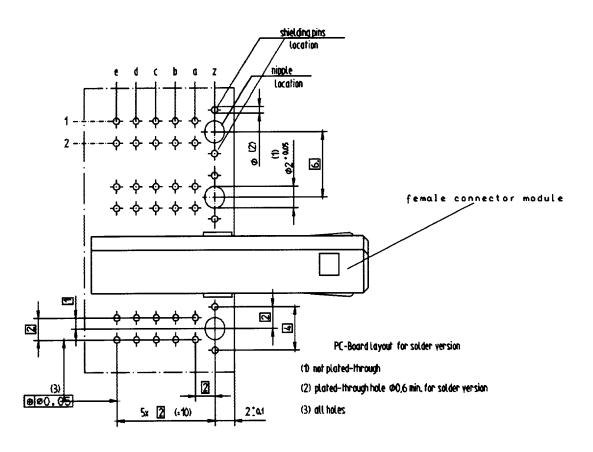

| Annex | M (Informative) DS-DE cable (10 core) recommendation                                                                                        | 131  |

| Annex | N (Informative) DS-DE multiway connector housing recommendation                                                                             | 132  |

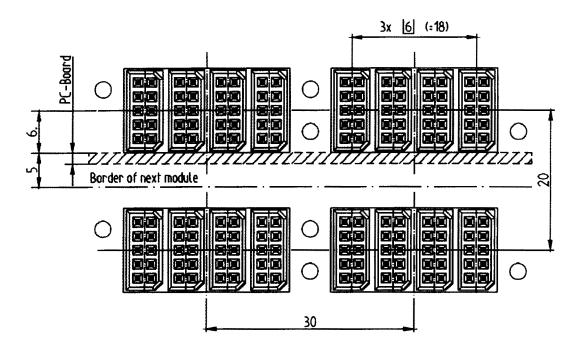

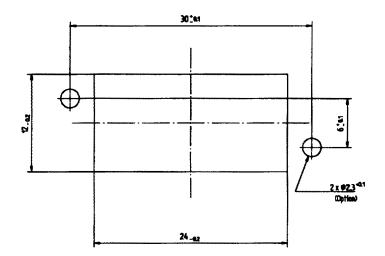

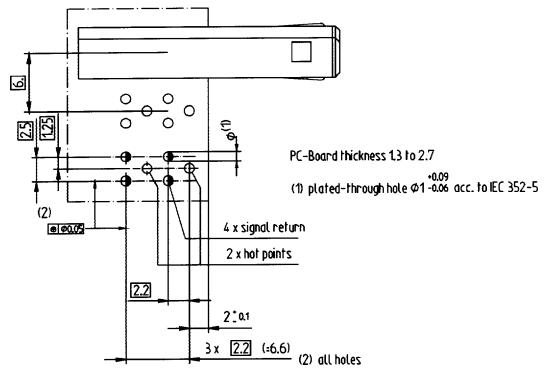

| Annex | O (Informative) HS-SE fixed connector PCB recommendation                                                                                    | 133  |

|       | P (Informative) HS-SE cable recommendation                                                                                                  |      |

|       | Q (Informative) HS-SE connector multiway housing recommendation                                                                             |      |

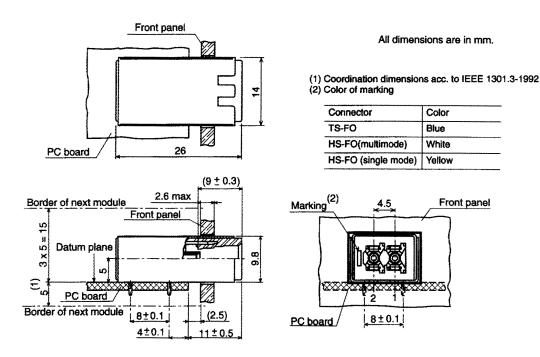

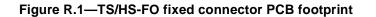

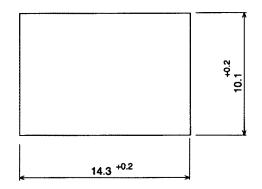

|       | R (Informative) TS/HS-FO connector PCB and front panel cut-out recommendation                                                               |      |

| Annex | S (Informative) TS/HS-FO fiber cable recommendation                                                                                         | 137  |

# IEEE Standard for Heterogeneous InterConnect (HIC) (Low-Cost, Low-Latency Scalable Serial Interconnect for Parallel System Construction)

# 1. Overview

# 1.1 Scope

The scope of this standard is the physical connectors and cables, electrical properties, and logical protocols for pointto-point serial scalable interconnect, operating speeds of 10–200 Mb/s and at 1 Gb/s in copper and optic technologies [as developed in Open Microprocessor Systems Initiative/Heterogeneous InterConnect Project (OMI/HIC)].

## 1.2 Purpose

The purpose of this standard is to enable high performance, scalable, modular, parallel systems to be constructed with low system integration cost; to support communications systems fabric; to provide a transparent implementation of a range of high level protocols [communications (e.g., ATM), message passing, shared memory transactions, etc.], and to support links between heterogeneous systems.

# 2. References

This standard shall be used in conjunction with the following publications:

CISPR 22: 1993, Limits and methods of measurement of radio disturbance characteristics of information technology equipment. <sup>1</sup>

DIN-VDE 0472-517, Testing of cables, wires cords; crosstalk attenuation.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>CISPR documents are available from the International Electrotechnical Commission, 3 rue de Varembé, Case Postale 131, CH 1211, Genève 20, Switzerland/Suisse. CISPR documents are also available in the United States from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

<sup>&</sup>lt;sup>2</sup>DIN documents are available from the Deutsches Institut Füer Normung DIN, Burggrafenstrasse 6, Posffach 1007, 12623 Berlin 30, Germany.

IEC 48B (Germany) 141, Time domain reflectrometry.

IEC 352-5: 1995, Solderless connections—Part 5.: Solderless press-in connections—General requirements, test methods and practical guidance.<sup>3</sup>

IEC 512-2:1985, Electromechanical components for electronic equipment; basic testing procedures and measuring methods—Part 2.: General examination, electrical continuity and contact resistance tests, insulation tests and voltage stress tests.

IEC 512-3:1976, Electromechanical components for electronic equipment; basic testing procedures and measuring methods—Part 3.: Current carrying capacity tests.

IEC 512-4 :1976, Electromechanical components for electronic equipment; basic testing procedures and measuring methods—Part 4.: Dynamic stress tests.

IEC 512-5 : 1992, Electromechanical components for electronic equipment; basic testing procedures and measuring methods—Part 5.: Impact tests (free components), static load tests (fixed components), endurance tests and overload tests.

IEC 512-6 : 1984, Electromechanical components for electronic equipment; basic testing procedures and measuring methods—Part 6.: Climatic tests and soldering tests.

IEC 512-7 : 1993, Electromechanical components for electronic equipment; basic testing procedures and measuring methods—Part 7.: Mechanical operating tests and sealing tests.

IEC 512-8 : 1993, Electromechanical components for electronic equipment; basic testing procedures and measuring methods—Part 8.: Connector tests (mechanical) and mechanical tests on contacts and terminations.

IEC 512-9 : 1992, Electromechanical components for electronic equipment; basic testing procedures and measuring methods—Part 9.: Miscellaneous tests.

IEC 793-1 :1992, Optical fibres—Part 1.: Generic specifications.

IEC 793-2 :1992, Optical fibres—Part 2.: Product specifications.

IEC 801-4 : 1988, Electromagnetic compatibility for industrial-process measurement and control equipment—Part 4.: Electrical fast transient/burst requirements (to be replaced by future IEC 1000-4-4).

IEC 825-1 : 1993, Safety of laser products—Part 1.: Equipment classification, requirements and user's guide.

IEC 825-2 : 1993, Safety of laser products—Part 2.: Safety of optical fiber communication systems.

IEC 917 : 1988, Modular order for the development of mechanical structures for electronic equipment practices.

IEC 1076-4-101 : 1995, Connectors with assessed quality for use in dc and low frequency analogue applications and in digital applications with high speed data rates. Part 4.: Printed board connectors—Section 101: Sectional specification.

IEC 1076-4-107 : 1995, Two part connectors for basic grid of 2.0 mm, with free connectors for nonaccessible insulation displacement termination.

<sup>&</sup>lt;sup>3</sup>IEC publications are available from the IEC Sales Department, Case Postale 131, 3, rue de Varembé, CH-1211, Genve 20, Switzerland/Suisse. IEC publications are also available in the United States from the Sales Department, American National Standards Institute, II West 42nd Street, 13th Floor, New York, NY 10036, USA.

IEC 1300 —, Fibre optic interconnecting devices and passive components—Basic test and measurement procedures.

IEC 1196-1 :1995, Radio-frequency cables—Specifications—Part 1.: Generic Specification, General Definitions, Requirements and Test Methods.

IEC 1196-2, Radio-frequency cables—Specifications—Semi-rigid radio-frequency and coaxial cables with polytetrafluoroethylene (PTFE) insulation—Sectional specification.

IEC 1754-6 :1995 [CDV document 86 B (Secretariat) 473], Fibre optic connector interfaces—Part 6.: Type MU connector family.

IEEE Std 100-1992, The New IEEE Standard Dictionary of Electrical and Electronics Terms (ANSI).<sup>4</sup>

IEEE Std 1301.3-1992, IEEE Standard for Metric Practice for Microcomputers—Convection Cooled with 2.5 mm Connector (ANSI).

QC 210000: 1987, Connectors for optical fibres and cables. Part 1.: Generic specification.<sup>5</sup>

# 3. Definitions

# 3.1 General

Common terms are as defined in IEEE Std 100-1992. <sup>6</sup> The terms defined in this clause are specific to this standard.

The word *shall* is used to indicate mandatory requirements strictly to be followed in order to conform with the standard and from which no deviation is permitted.

The word *should* is used to indicate that among several possibilities one is recommended as particularly suitable, without mentioning or excluding others; or that a certain course of action is preferred but not necessarily required; or that (in the negative form) a certain course of action is deprecated but not prohibited.

The word *may* is used to indicate a course of action:permissible within the limits of the standard.

#### 3.2 Glossary

#### **3.2.1 BER**: *See:* bit error rate.

**3.2.2 bit error rate:** The ratio of errors to the total number of bits being sent in a data transmission from one location to another.

**3.2.3 box:** A mechanical unit that contains links; the links may either remain inside the box, connecting internal devices, or may leave the box in order to connect internal devices to external ones. A box is assumed to be an EMC compliant enclosure and to operate under a single electrical environment.

<sup>&</sup>lt;sup>4</sup>IEEE publicatons are available from the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA.

<sup>&</sup>lt;sup>5</sup>*This publication also bears the number IEC 874-1.* QC 210000 is available from International Electrotechnical Commission, IEC publications are available from IEC Sales Department, Case Postale 131, 3, rue de Varembé, CH-1211, Genève 20, Switzerland/Suisse. IEC publications are also available in the United States from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

<sup>&</sup>lt;sup>6</sup>Information on references can be found in clause 2.

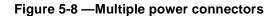

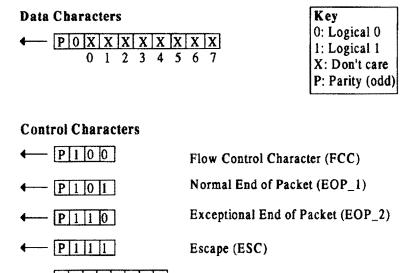

**3.2.4 character:** A group of consecutive bits used to represent control or data information. Characters are of two types: normal characters (N\_chars) or link characters (L\_chars). *See also*: **control character, data character, link character, normal character.**

**3.2.5 character layer:** The layer of the protocol stack that specifies the representation of characters in terms of groups of consecutive bits. The character layer provides the service to the higher layers of the transmission of a continuous sequence of characters on a link.

**3.2.6 coding:** The translation from the original set of bits (character) to a new set of bits (coded character) suitable for serial transmission. *See also*: **decoding**

**3.2.7 control character:** A character used for signaling purposes by the exchange, packet or transaction layers of the stack. Both N\_chars and L\_chars are used as control characters. *See also:* **link character; normal character.**

**3.2.8 data character:** A character used for packet payload or packet header. A data character represents one of the values of a byte, i.e., 0—255 (decimal). Only N\_chars are used as data characters. *See also:* link character; normal character.

**3.2.9 decoding:** The translation from the coded set of bits (coded character) to the original set of bits (character). *See also:* coding.

**3.2.10 deserialization:** The assembly of a coded character from the sequence of serial bits. *See also:* serialization.

**3.2.11 destination:** One or more destination\_identifiers, identifying the destination node(s) to which the packet is to be transmitted. *See also:* **destination\_identifier.**

**3.2.12 destination\_identifier** (dest\_id): An implementation dependent identity of a destination node for a packet.

3.2.13 destination node: The terminal node(s) that is/are to receive a particular packet. See also: node.

**3.2.14 digital sum variation:** The difference between the number of logical ls and the logical Os transmitted by a link output since commencing operation. *See also:* **running disparity.**

**3.2.15 disparity:** The difference between the number of logical 1s and logical 0s in a character. A positive or negative disparity indicates an excess of 1s or 0s, respectively.

3.2.16 end\_of\_packet marker: A control character that indicates the end of a packet. See also: packet.

**3.2.17 exchange layer:** The exchange layer describes the procedure of the node-to-node exchange of characters to ensure the proper functioning of the link. The exchange layer provides the service to the higher layers of the transmission of an indefinite sequence of  $N_{chars}$ .

**3.2.18 fabric:** A device or a collection of devices that provides a general routing capability, constructed from one or more switches using links. *See also:* link; switch.

**3.2.19 flow control character (FCC):** A control character transmitted on a link in the opposite direction to data flow for each direction of data flow, i.e., to the transmitter of data from the receiver, indicating that the receiver has space reserved to receive a further F N\_chars. The value of F is specified separately for each technology in this standard.

**3.2.20 functional:** A link interface becomes functional when the start-up procedure has successfully completed and the link interface is ready to transmit data.

**3.2.21 link:** A means of communicating digital information bidirectionally in serial format between two devices or subsystems. A link comprises two link interfaces connected by an appropriate medium (or media, for connections between boards or cabinets), such that the link output of each interface is connected to the link input of the other.

**3.2.22 link cable:** The physical medium connecting two link interfaces, comprising of two or more electrical or optical cables.

**3.2.23 link character (or L\_char):** Control characters that are used on a link in order to ensure flow control and the proper functioning of the link. *See also:* normal character.

3.2.24 link input: A connection point for receiving signals. See also: link interface.

**3.2.25 link interface (or port):** A connection point comprising a link input and a link output and implementing one of the relevant conformance subsets defined in 10.2. *See also:* **link.**

3.2.26 link output: A connection point for transmitting signals. See also: link interface.

**3.2.27 network:** Any set of devices or subsystems connected by links joining (directly or indirectly) a set of terminal nodes.

**3.2.28 node:** A device or subsystem having one or more link interfaces. A node may be a terminal node (q.v.). A node may perform a muting function, muting packets between its node interfaces according to the information in the destination field of the packet.

3.2.29 node interface: A link interface on a switch. See also: link interface; switch.

**3.2.30 normal character (or N\_char):** N\_chars represent, at the minimum, the 256 values of a byte (i.e., all the data characters) plus a control character representing an end\_of\_packet marker.

**3.2.31 packet:** A sequence of N\_chars with a specific order and format. A packet consists of a destination followed by a payload. A packet is delimited by an end\_of\_packet marker. *See also:* destination; payload.

**3.2.32 packet layer:** The layer of the protocol concerned with end-to-end transmission of information, possibly through a number of intermediate routers. It is at the packet layer that the muting decisions are taken.

**3.2.33 payload:** The data (a message, a memory access request, an acknowledgment, etc.) that is to be transferred from the source node to the destination node. It has a specific format, defined in the transaction layer. Note that a payload may be null. *See also:* **packet.**

3.2.34 physical medium: See: transmission medium.

**3.2.35 port:** *See:* link interface.

**3.2.36 routing function:** Inside a switch, this is function that determines to which numbered node interface a packet is to be sent, based on the information contain in the packet destination. *See also:* switch.

**3.2.37 run length:** The maximum number of successive bits of the same value that can occur in the coded 3.2.37 run length: The maximum number of successive bits of the same bit stream.

**3.2.38 running disparity:** The cumulative sum of the disparities of characters transmitted from the start of operation of the link up to the present time. A link has two running disparities, one for each direction.

3.2.39 serialization: The process of transmitting coded characters one bit at a time. See also: deserialization.

**3.2.40 signal:** A measurable quantity (e.g., a voltage) that varies in time in order to transmit information. A signal propagates along a wire or an optic fiber. It is interpreted as a sequence of bits that is grouped into a sequence of characters by the character layer of the protocol stack. Signals are generated by a link output and are absorbed by a link input.

**3.2.41 signal layer:** The layer of the protocol stack at which signals are specified.

3.2.42 sink: A consumer of normal characters at a link interface. See also: normal character.

3.2.43 source: A generator of normal characters at a link interface. See also: normal character.

3.2.44 source node: A terminal node that originates data. See also: destination node

**3.2.45 switch:** A routing device (for example, a box or board) providing a set of numbered node interfaces, constructed from one or more switch chips (or by other methods). *See also:* **fabric, node interface, switch chip.**

**3.2.46 switch chip:** A VLSI integrated circuit with two or more link interfaces, between which it provides packet routing. *See also:* **link; switch.**

**3.2.47 terminal node:** A node with one or more link interfaces that are used to originate or consume data across an interconnect complying with this standard. *See also:* **source; sink.**

**3.2.48 transaction:** A sequence of packets sent between two or more terminal nodes to perform some function. *See also:* transaction layer.

**3.2.49 transaction layer:** The layer above the packet layer for use by applications. It is unspecified in this standard. *See also:* transaction.

3.2.50 transmission medium: A means of transporting electrical or optical signals. See also: signal.

# 4. Physical media and logical layers

This standard defines a set of rules for information exchange (the logical layers) together with the ways in that it shall be implemented on a variety of physical media. The logical layers are defined as a protocol stack. Each layer of the protocol stack defines representations (information formats) in terms of the immediately lower layer, together with rules (protocols) for the exchange of these representations.

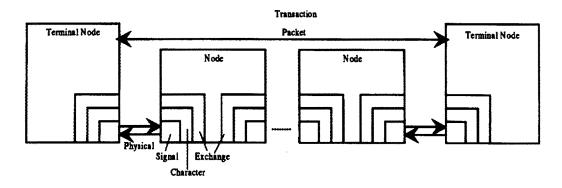

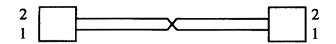

The use of the physical media and logical layers is illustrated in figure 4-1. The physical medium and the signal, character and exchange layers are concerned with point-to-point communication between adjacent nodes, while the packet layer provides end-to-end communication between terminal nodes.

Figure 4-1 — Protocol stack between nodes

# 4.1 Physical media

For electrical links, the physical characteristics include the specification of

- a) Circuit board physical characteristics

- b) Connectors and contacts

- c) Cables

- d) Shielding requirements

- e) Line impedance

- f) Crosstalk

- g) Electromagnetic emission

- h) ESD susceptibility

For optical links, the physical characteristics include the specification of

- Optical transceiver properties

- Optical connectors

- Optical fiber

# 4.2 Logical layers

## 4.2.1 Layer 0: signal layer

## 4.2.1.1 General description

For electrical links, the signal layer includes the specification of

- a) Line signal levels and rates

- b) Power budget, from which transmission distance may be calculated, taking into account the loss from the cables and connectors

- c) Noise margins

For optical links, the signal layer includes the specification of

- Spectral center wavelength, aperture

- Optical power budget

It is important to note that there is a difference between signals and bits. Signals are the values of a measurable quantity (e.g., voltage levels) that are on the transmission line; bits are the logical ls and Os that the signals represent. The measurable quantities vary both in nature and in value depending on the implementation (CMOS, ECL, CML, light pulses on a fiber optic cable, etc.).

The signals may have various properties, such as limited running disparity, limited run length, and/or dc balance, over a period of time.

## 4.2.2 Layer 1: character layer

## 4.2.2.1 Definition of character

Bits are transmitted in groups called characters. The character layer provides the service to the higher layers of the transmission of a continuous sequence of characters on a link.

## 4.2.2.2 General description

Characters are used by the higher layers of the protocol to communicate both data information and control information. The number and representations of the various control characters and the representations of the 256 possible data values varies according to the different types of links specified in this standard.

#### 4.2.3 Layer 2: exchange layer

## 4.2.3.1 Definition of the exchange layer

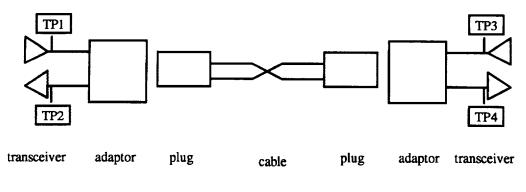

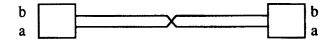

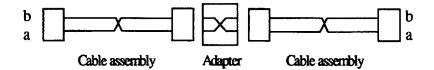

A link is the means of communicating digital information bidirectionally in serial format between two very large scale integration (VLSI) devices. A link comprises two link interfaces connected by an appropriate medium (or media, for connections between boards or cabinets), such that the link output of each link interface is connected to the link input of the other.

The exchange layer describes the procedure of the node-to-node exchange of characters to ensure the proper functioning of the link.

## 4.2.3.2 General description

Two types of character are defined: link character (L\_char) and normal character (N\_char).

- a) L\_chars: L\_chars are used on a node-to-node link in order to ensure flow control and the proper functioning of the link.

- b) N\_chars: N\_chars represent, at the minimum, the 256 values of a byte plus an end\_of\_packet marker. The exchange layer provides the service to the higher layers of the transmission of an indefinite sequence of N\_chars. It is specified in such a way as to ensure that N\_chars are not lost due to limitations of resources (e.g., lack of available buffer space).

L\_chars may be arbitrarily interleaved with N\_ehars on the link as required by the exchange layer.

Note that in the text of this standard the data values of a byte (0 to 255) are referred to as data characters, and all the other used characters (i.e., all L\_chars and the remainder of the N\_chars) as control characters.

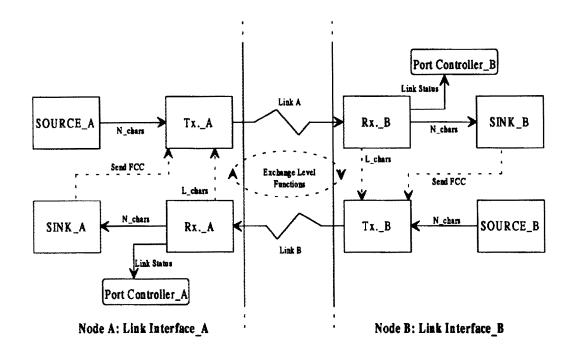

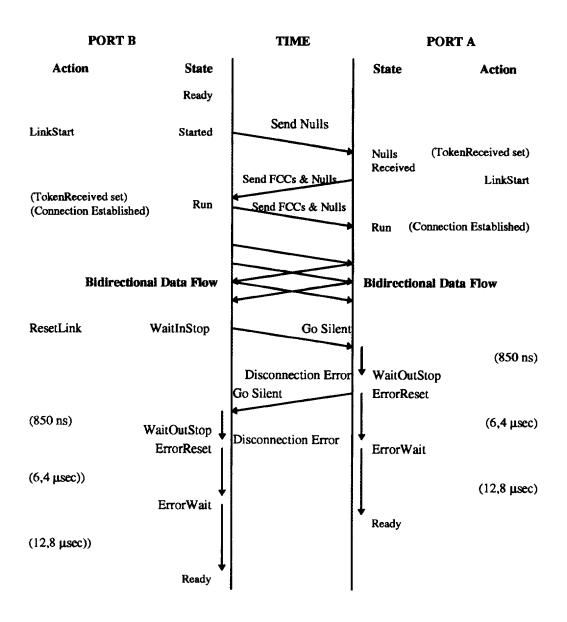

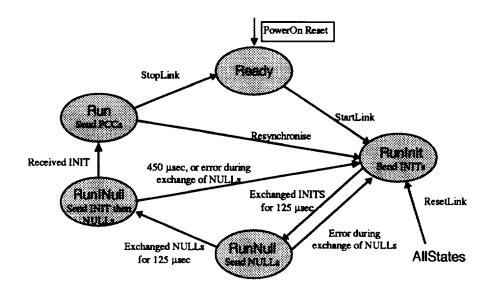

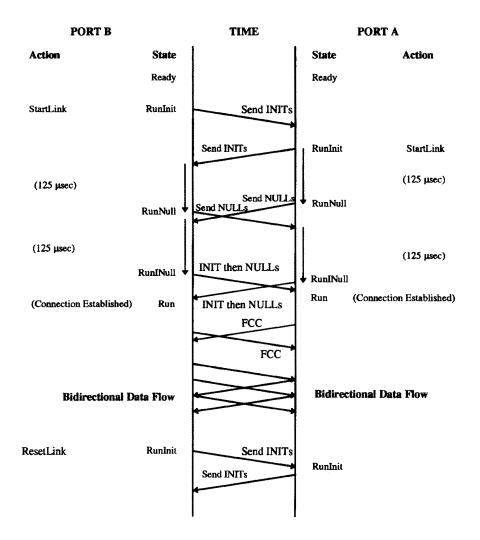

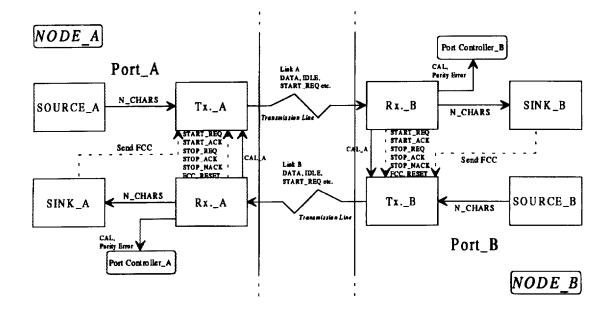

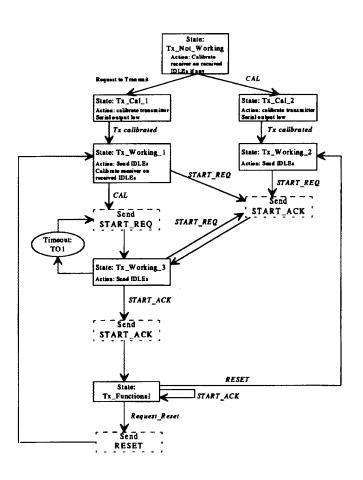

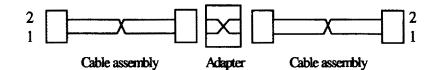

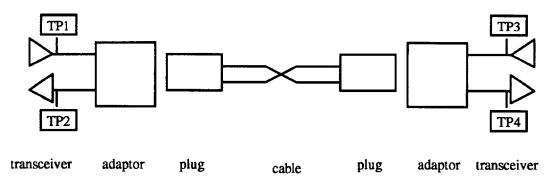

Consider two connected nodes, NODE\_A and NODE\_B (see figure 4-2). Each node uses a link interface or port (LINK\_INTERFACE\_A and LINK\_INTERFACE\_B respectively) in order to communicate with the other node. Note that a node may have more than one link interface. Each link interface is divided into two parts: a transmitter and a receiver, referred to as transmitter\_A and receiver\_A for NODE\_A and transmitter\_B and receiver\_B for NODE\_B.

Each link interface has a N\_char source (SOURCE\_A and SOURCE\_B) that supply Nchars to transmitter\_A and transmitter\_B respectively and a N\_char sink (SINK\_A and SINK\_B) that accept data from receiver\_A and receiver\_B respectively.

Exchange layer information generated and sent, for example, by transmitter\_A are received and filtered by the receiver\_B and passed directly to transmitter\_B (and vice-versa). L\_chars shall not be generated by the source nor written into the sink.

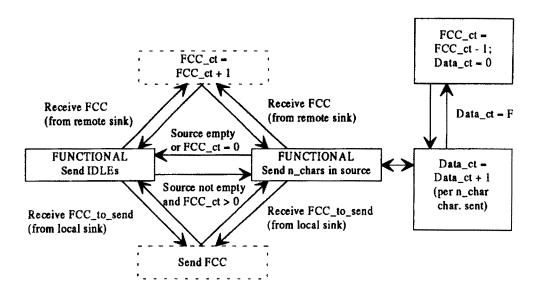

# 4.2.3.3 Flow control

The N\_char sink associated with a link interface has a maximum capacity, defined by the physical implementation. N\_chars are written into the sink by the receiver as it receives them at the link interface, and are read from the sink by the application using the link. In order to prevent sink overrun a flow control mechanism shall be implemented.

The source (at the other end of the link) maintains a "credit" associated with the receiving link interface that indicates how many N\_chars the source can transmit over the link without overrunning the sink at the receiving end. For every N\_char that the source sends, it shall decrement the credit by one. When the credit reaches zero, the source shall not send any further N\_chars, but it may continue to send L\_chars. The credit maintained by the source shall be increased by a block value (sometimes referred to as a "flit") of F characters when the source receives a Flow Control Character (FCC) from the opposite receiver. If this happens when the credit was zero (which will have inhibited the transmission of N\_chars), then the source may recommence transmitting N\_chars. An implementation may restrict the amount of credit that a source can record. If a FCC is received when this credit has its maximum value, the FCC may be discarded (ignored) without affecting the operation of the link. A source shall be able to record at least F N\_chars of credit.

The initial value of the credit shall be O. The block size (value of F) is defined as a function of the technology used.

The sink should send a FCC to the source when it has the space to receive F N\_chars. Each time the sink authorizes the sending of a FCC it shall reserve the space corresponding to F N\_chars. While the sink has unreserved space available it should send FCCs until all its space associated with the link interface is reserved. One of the first actions of each sink after the link has been started from a reset condition should therefore be to send the number of FCCs corresponding to its unreserved space.

Using the flow control mechanism described above, there exists a theoretical maximum line length over which "continuous transmission" can be obtained in the case where every N\_char written into the sink is immediately read out of the sink by the receiving application. This maximum length is determined by the size of the sink (which determines the number of PCCs that the receiver sends to the transmitter after the link has been started from a reset

condition and thus the initial transmitter credit) and a number of implementation-dependent parameters. This is detailed in annex H.

Figure 4-2 — Exchange layer

Exchange layer flow control greatly simplifies the higher layers of the protocol, since it prevents data from being lost due to buffer overflow and so removes the need for re-transmission unless errors occur. To the user of the system, the net result is that a link functions as a pair of fully handshaken first-in, first-outs, one in each direction.

Note that the link interface regulates the flow of data items without regard to the higher layer objects that they may constitute. At any instant the N\_chars buffered by a link interface may form part or all of one or more consecutive higher layer objects. L\_chars, including FCC, do not belong to such objects and are not buffered.

#### 4.2.4 Layer 3: packet layer

#### 4.2.4.1 Definition of a packet

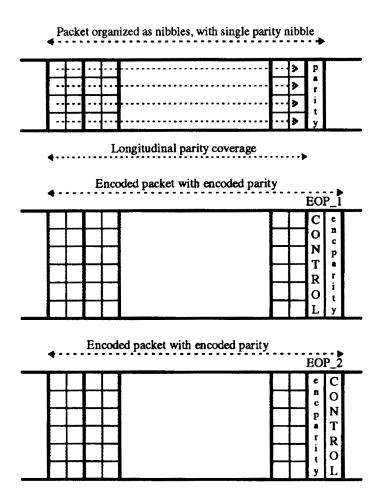

A packet is a sequence of characters (N\_chars only) with a specific order and format. Constituent characters of different packets shall not be interleaved on a link. A packet consists of a *destination* followed by a *payload*. A packet is delimited by an end\_of\_packet marker.

#### 4.2.4.2 General description

Terminal nodes generate (source node) and consume (destination node) packets. A network is any set of devices connected by links joining (directly or indirectly) a set of terminal nodes.

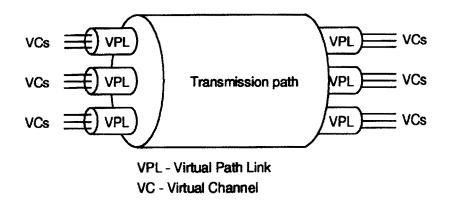

The protocol assumes the use of packet-switched networks in which the routing information necessary to correctly transmit the packet across the network is contained in the first K N\_chars of the packet (where K is fixed throughout a subnetwork). It is at the packet layer that the routing decisions are taken. The protocol does not define a specific (or maximum) size for a packet. Successive packets transmitted on a link may have different lengths and/or destinations.

Each packet is transmitted in its entirety, i.e., the transmission of a packet on a link shall be completed before the transmission of the successive packet may commence. Packets sent from a given source node to a given destination node over a network may be delivered in an order different from the sending order. The details of mechanisms to ensure in-order delivery are outside the scope of this standard.

# 4.2.4.3 Destination

The destination contains one or more destination identifiers (dest\_id) that are used as the input to the routing function, enabling the routing network to transit the packet from its source node to its destination node. The destination could be null for specific case of a point-to-point link (i.e., the network is just one link). More than one dest\_id may denote the same destination node. The method of allocating dest\_ids to destinations is outside the scope of this standard. See also clause 9. and annex E.

# 4.2.4.4 Payload

The payload is the data (a message, a memory access request, an acknowledgment, etc.) that has to be transferred from the source node to the destination node. It has a specific format, defined in the transaction layer. Note that a payload may be null.

# 4.2.4.5 End of packet marker

A packet is delimited by an end of packet marker.

# 4.2.5 Layer 4: transaction layer

A transaction is a sequence of packets sent between two or more terminal nodes to perform some function. At this layer there are two concepts:

- a) Definition of the specific payload formats necessary to perform the function

- b) Definition of the sequence of exchanges of packets necessary to perform required function

The definition of any form of transaction is outside the scope of this standard. Annexes F and I illustrate the use of the transaction layer.

# 4.3 Interaction of layers

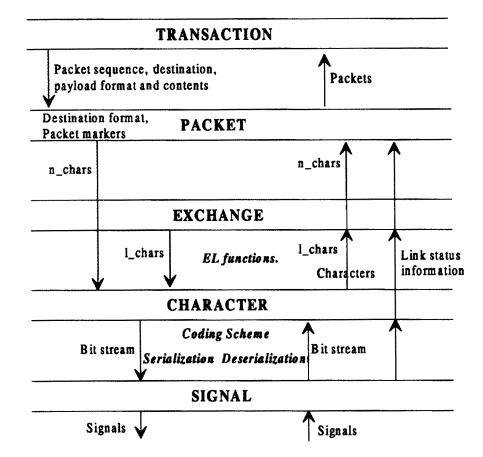

The interaction of the layers is illustrated in figure 4-3.

Figure 4-3 — Protocol stack diagram showing interaction of layers

#### 4.3.1 "Downward going"

#### 4.3.1.1 Transaction layer to packet layer

The transaction layer provides packets to the packet layer. The packet sequence, payload contents and destination address(es) are all determined by the transaction layer. The packet layer forms the packet destination from the destination address(es) and appends the packet with the appropriate end\_of\_packet marker.

#### 4.3.1.2 Packet layer to exchange layer

The packet layer provides the sequence of N\_chars that forms each packet to the exchange layer.

#### 4.3.1.3 Exchange layer to character layer

The exchange layer passes the N\_chars that have been provided to it by the packet layer onto the character layer. In order to perform the exchange layer functions, it intefieaves L\_chars arbitrarily into the sequence of N\_chars. The sequence of N\_chars is unchanged.

## 4.3.1.4 Character layer to signal layer

The character layer translates the characters (N\_chars and L\_chars) it receives from the exchange layer into a bit stream that it passes to the signal layer. The translation is formed of two parts: coding and serialization. Coding is the translation from the original set of bits (character) to a new set of bits (coded character) suitable for serial transmission. Serialization is the process of transmitting coded characters one bit at a time.

#### 4.3.1.5 Signal layer

The signal layer takes the bit stream and outputs signals onto the physical medium.

#### 4.3.2 "Upward Going"

#### 4.3.2.1 Signal layer to character layer

At the receiver end, the signal layer receives signals from the line and generates the corresponding bit stream.

#### 4.3.2.2 Character layer to exchange layer

The character layer descrializes and decodes the bit stream to produce a sequence of characters. Descrialization is the assembly of a coded character from the sequence of serial bits. Decoding is the translation from the coded set of bits (coded character) to the original set of bits (character). The characters are passed to the exchange layer.

#### 4.3.2.3 Exchange layer to packet layer

The exchange layer filters out L\_chars for exchange layer functions and passes the N\_chars to the packet layer.

#### 4.3.2.4 Packet layer to transaction layer

The packet layer reconstitutes the packets from the received N\_chars. This is a logical reconstitution and need not imply that a whole packet is physically assembled. Routing functions are carried out at the packet layer, based on the information in the packet destination. When necessary (e.g., when a packet has arrived at its destination node), the packets are delivered to the transaction layer.

#### 4.3.2.5 Link status information

Link status information is passed up between the layers from the signal layer to the packet layer. The link status information necessary is dependent on the implementation of the link and includes, for example, information on the calibration of the receiver, parity errors, etc. It is for each layer to filter the information that is relevant to its functioning and to pass up the remaining information.

## 4.4 Implementations defined in the standard

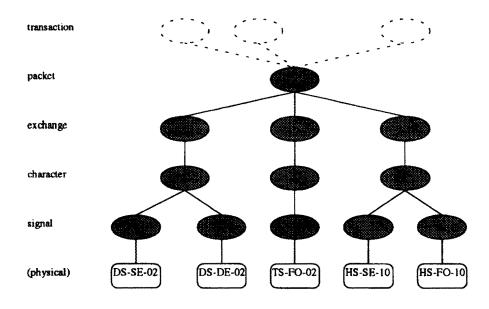

The physical and logical layers defined in this standard are illustrated in figure 4-4.

The physical layer may be implemented in a number of different technologies, identified according to signaling convention, transmission medium, and maximum operating speed.

The format for this identification is given by three parameters:

#### SC-TM-dd

The possible values of these parameters are given in table 4-1.

Table 4-2 provides the major properties of each of the defined implementations.

Figure 4-4 — Defined implementations of physical and logical layers

| Parameter | Values                                                                      | Description                          |  |  |  |  |

|-----------|-----------------------------------------------------------------------------|--------------------------------------|--|--|--|--|

|           | DS                                                                          | Data/strobe encoding                 |  |  |  |  |

| SC        | TS                                                                          | Three-of-six encoding                |  |  |  |  |

|           | HS                                                                          | High speed encoding                  |  |  |  |  |

|           | SE                                                                          | Single-ended electrical transmission |  |  |  |  |

| ТМ        | DE                                                                          | Differential electrical transmission |  |  |  |  |

|           | FO                                                                          | Fiber optic transmission             |  |  |  |  |

| dd        | Two digits, representing the maximum operating speed<br>in units of 100 MBd |                                      |  |  |  |  |

Table 4-1 — Identification format for technologies

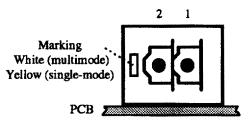

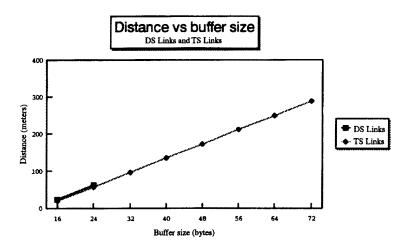

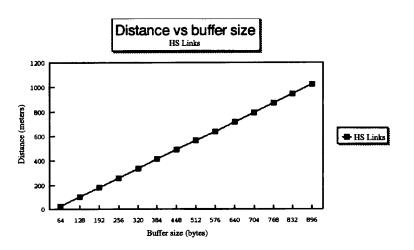

DS-SE links are intended for use for chip-to-chip and board-to-board interconnect. This standard does not therefore specify any cable/connector system for these links. DS-DE links are intended for interconnecting sub-racks and adjacent racks using a protocol compatible with DS-SE link from the character layer upwards. TS-FO links are intended to provide longer distance transmission using, necessarily, optical technology, but at speeds compatible with DS-SE links. The use of optical technology necessitates some differences at the exchange layer. HS-SE links are intended for high speed rack-to-rack interconnect. They can, of course, also be used between chips and between boards (across a backplane), given suitable attention to maintaining appropriate signal integrity. HS-FO links are intended to provide longer distance transmission using a protocol compatible with HS-SE links from the character layer upwards.

This standard specifies an appropriate cable/connector system for each of the technologies specified within this standard, with the exception of DS-SE links. The connector system is intended as a front-panel adapter and matching cable mounted connector.

| Technology | Baud Rate   | Maximum<br>bidirectional<br>data rate | Type of transmission<br>(full duplex) | Maximum<br>distance | Connector<br>specification |

|------------|-------------|---------------------------------------|---------------------------------------|---------------------|----------------------------|

| Units      | Baud        | MByte/s                               | _                                     | Meters              | —                          |

| DS-SE-02   | 1.333-200 M | 38                                    | 4 wires                               | 1                   | None                       |

| TS-FO-02   | 250 M       | 39.4                                  | 2 multimode fibers                    | 300                 | IEC 1754-6                 |

| DS-DE-02   | 1.333-200 M | 38                                    | 8 wires                               | 10                  | IEC 1076-4-107             |

| HS-SE-10   | 700-1 000 M | 160                                   | 2 coax cables                         | 8                   | IEC 1076-4-107             |

|            |             |                                       | 2 62.5 μm multimode<br>fibers         | 100                 | IEC 1754-6                 |

| HS-FO-10   | 700-1 000 M | 160                                   | 2 50 μm multimode<br>fibers           | 1 000               | IEC 1754-6                 |

|            |             |                                       | 2 single-mode fibers                  | 3 000               | IEC 1754-6                 |

#### Table 4-2 — Defined implementations

This standard does not specify any backplane or mezzanine connector standards. This is considered more appropriately specified as an adjunct to specific existing backplane standards.

# 5. DS-SE and DS-DE

# 5.1 General

The DS-SE and DS-DE links are designed for point-to-point communication that may be on a single PCB, board to board (DS-SE links), or box to box (DS-DE links). Since this implies that transmission line problems might be present, the electrical level is specified as a transmission line system. In order to reduce the power required for each link (permitting single chips to have a large number of link ports) source-only termination is used for DS-SE links.

A DS-SE/DS-DE input is self-clocking, which means that in any particular system the actual operating speed may be chosen to suit the system, rather than the more normal case of having to engineer a system to suit a pre-determined transmission speed. The maximum speed at which it may run is a function of the maximum speed of the circuitry at each end, plus the properties of the medium connecting the two ends. A link may be operated at lower speeds, for example to provide power saving, down to a level at which the disconnection detection mechanism is triggered.

A link shall operate at a speed of 10 MBd unless and until the system in which it operates determines that it may operate at a different speed. The electrical specification of the link has been designed to allow operating speeds of up to 200 MBd, but the actual operating speed is left open to allow the design of any particular system to trade off engineering costs against operating speed. The means of setting the speed of a link is not defined within this standard.

# 5.2 DS-SE: physical medium

## 5.2.1 Transmission line requirements

For distances greater than a few centimeters, signal integrity considerations dictate that the link line has to be considered as a transmission line. Discontinuities or variations in characteristic impedance should be kept to a minimum. The transmission line may be made on PCBs but care shall be taken to provide a good ground or power plane beneath the link track and crosstalk with other tracks should be minimized (including between data and strobe

lines of the same link). The longest length of line achievable will depend on the materials used for interconnect and the grounding arrangements.

DS-SE supports two standard nominal characteristic impedances for the physical medium, 50  $\Omega$  and 100  $\Omega$  Drivers conforming to the DS-SE electrical standard shall support one of these impedances and may support both. Each direction (i.e., the data and the strobe line) of a single point-to-point link shall use either one or other impedance throughout the length of the link and use a matched driver. The opposing directions of a single point-to-point link may however use different impedances.

# 5.3 DS-SE signal level

# 5.3.1 General

Each connection of a DS-SE link shall be implemented as a unidirectional point-to-point transmission line. The transmission line shall have a characteristic impedance of either 50  $\Omega$  or 100  $\Omega$  and shall be terminated by high impedance at the receiver. The transmission line may be provided by PCB, coax or other suitable controlled impedance interconnect. The receiver shall be designed to accept standard TTL input switching levels with a high input impedance. The driver output impedance should be close to the characteristic impedance of the transmission line both when the driver is driving low or high and also while switching. This is to ensure that reflections generated by the receiver are sufficiently damped by the driver that they do not cause spurious transitions. The range 0.8 V to-2.0 V at the receiver is defined as the transition region. It is very important that the signal at the receiver is monotonic in the transition region, and that the reflections do not cause spurious transitions. This should be ensured by careful design of the interconnect and the driver output.

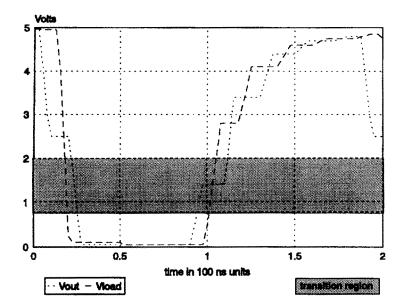

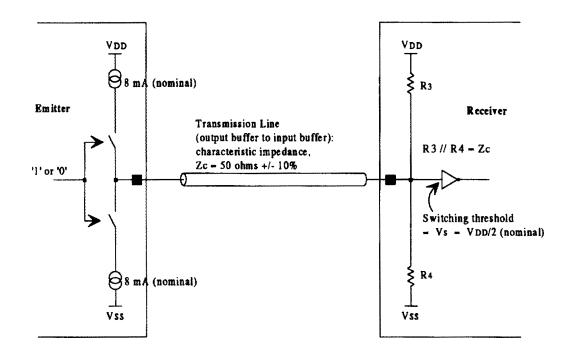

The propagation of signals is as follows. Assuming that the line is in a steady-state low condition, a high going transition is output by the driver. Because of the relatively high output impedance of the driver compared to the line, this is attenuated, typically to a level of about 1.4 V at the driver output. At the receiver, the high input impedance of the receiver (effectively an open circuit) causes this to appear as a 2.8 V step (taking the input cleanly through the transition region), and the reflection travels back down the line to the driver. Depending on how closely the driver output impedance is matched to the line, this may cause further reflections: it is crucial that the driver is matched sufficiently well that these reflections do not cause spurious transitions at the receiver, or interfere with subsequent output transitions. Propagation for a low-going transition is similar. Figure 5-1 shows example, waveforms for the driver and the receiver end of the transmission line for a 100  $\Omega$  system operating from a 5 V supply.

Note that the signal levels at the receiver and the specification of the driver allows DS-SE links to be interconnected between devices operating from 5 V and 3.3 V supply rails as long as the inputs of the 3.3 V devices are tolerant of 5 V signals.

## 5.3.2 DS-SE link driver

Each driver should have a nominal output impedance of either 50  $\Omega$  or 100  $\Omega$  depending on the transmission medium to terminate the reflections from the receiver. The output impedance shall be controlled when the output is fully on driving a high or low level, and also while switching. In order to be adequately matched, the characteristics of the driver and the transmission line shall be related as shown in the table 5-1.

|           |       |      | $\mathbf{Vdd} = 3.0$ | V to 3.6 V |      |      | Vdd = 4.5 | V to 5.5 V |         |  |  |

|-----------|-------|------|----------------------|------------|------|------|-----------|------------|---------|--|--|

|           |       | Z    | 'n                   | Z          | р    | Z    | 'n        | Z          | р<br>Др |  |  |

|           | Units | Min. | Max.                 | Min.       | Max. | Min. | Max.      | Min.       | Max.    |  |  |

| Zo=45-55  | ohms  | 29   | 56                   | 37         | 67   | 32   | 52        | 55         | 123     |  |  |

| Zo=90-110 | ohms  | 58   | 112                  | 73         | 135  | 64   | 104       | 110        | 247     |  |  |

Table 5-1 — Driver to line impedance matching table

Figure 5-1 — DS-SE link signal propagation

Zo is the characteristic impedance of the transmission line. Zn is the impedance of the driver when the output is driving low, and Zp the impedance when it is driving high. The figures depend on the supply voltage used by the driver because the input threshold is fixed.

It is recommended that nominal 50  $\Omega$  characteristic impedance transmission lines be used in nominal 3.3 V systems and on backplanes.

On power on and reset, a DS-SE !ink output shall hold both the data and strobe signals low.

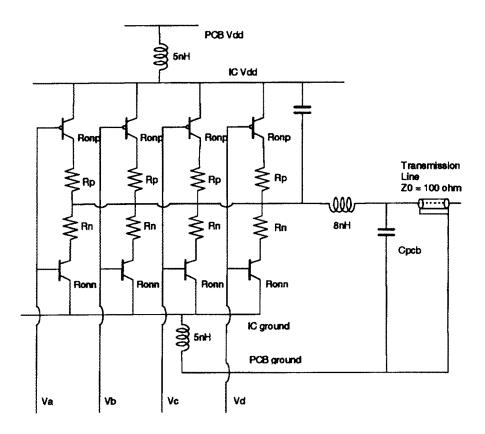

Annex J gives an example DS-SE link driver circuit for a 100  $\Omega$  transmission line with 5 V supplies.

## 5.3.3 DS-SE link receiver

A DS-SE link input shall present a high impedance termination to the transmission line. An impedance of >10 k $\Omega$  is recommended. This high input impedance is essential to ensure that the correct signal levels are produced at the receiver input.

The input threshold of the receiver is nominally 1.4 V and shall be within the transition region, which is defined as 0.8-2.0 V.

The input capacitance is modelled as described in 5.3.4 (see figure 5-2) and specified in table 5-2.

| Symbol | Parameter         | Units | 100 MBd |      | 100 MBd |      | 200 ] | Notes |  |

|--------|-------------------|-------|---------|------|---------|------|-------|-------|--|

|        |                   |       | Min.    | Max. | Min.    | Max. | Min.  | Max.  |  |

| Ci     | Input capacitance | pF    |         | 300  |         | 30   |       | 4     |  |

| Table 5-2 — DS-S | SE input c | apacitance |

|------------------|------------|------------|

|------------------|------------|------------|

#### 5.3.4 DS-SE link timing

A link shall operate at a speed of I0 MBd, until the system in which it operates shall determine it may operate at a different speed. A link may be operated at a speed lower than its nominal speed to suit the transmission medium. If a link is operated at a lower speed, the same timing constraints shall apply at the receiver inputs.

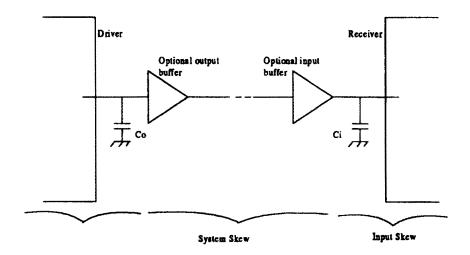

DS-SE parameters are relative to a reference model, as shown in figure 5-2.

Figure 5-2 — DS-SE timing reference model

This model shows the possibility of buffers in the signal path, in which case the output impedance of the second buffer is assumed to be not more than 100  $\Omega$  and Co is assumed to be not more than Ci. If buffers are not used then Ci and Co are combined into a single capacitive load that may be twice the figure given in table 4. If the output drivers are matched to 100  $\Omega$  and it is required to use 50  $\Omega$  transmission lines, then buffers will be required.

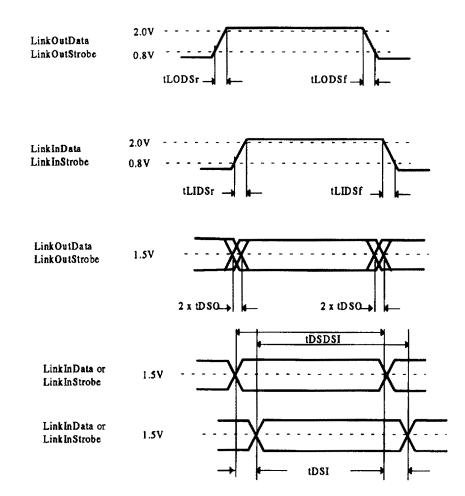

Three sets of timing parameters are defined (see table 5.3 figure 5-3), to allow for operation at the default speed of 10 MBd (DS-SE-00 links), 100 MBd (DS-SE-01 links), and 200 MBd (DS-SE-02 links). A higher speed link type will always be able to operate at a lower speed.

| Symbol | Parameter                    | Units 10 MBd |      | 100 MBd |      | 200MBd |      | Notes |     |  |

|--------|------------------------------|--------------|------|---------|------|--------|------|-------|-----|--|

|        |                              |              | Min. | Max.    | Min. | Max.   | Min. | Max.  |     |  |

| tDSI   | D/S edge min. separation     | ns           | _    | 20      | _    | 2.5    | _    | 1     | 1.2 |  |

| tDSDSI | Sustainable input bit period | ns           | 80   | 750     | 9    | 750    | 4.5  | 750   | 3   |  |

| tLIDSf | Input fall time (2.0–0.8 V)  | ns           |      | 100     | _    | 100    |      | 100   | 4   |  |

| tLIDSr | Input rise time (0.8–2.0 V)  | ns           | _    | 100     | _    | 100    |      | 100   | 4   |  |

Table 5-3 — DS-SE timing and swings

#### NOTES

1-tDSI is the minimum separation between consecutive edges on the data and strobe inputs (one edge of either sense on each wire) that the link can discriminate correctly. An implementation shall not require this to be greater than the appropriate value specified in table 5-3.

2-The same figure applies to consecutive edges of opposite sense on either the data or the strobe input.

3—In general a link input cannot handle a continuous stream of edges separated by tDSI. This figure specifies the sustained bit period that shall be accepted for the nominal baud rate. The maximum nominal bit time is determined by disconnect time-out period of the link receiver.

4-This is the slowest edge that the input shall accept.

Figure 5-3 — DS-SE link timings

The output skew is determined by parameters given in table 5-4.

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                               | Parameter                    | Unit | 10 N | ABd  | 100  | MBd  | 200  | MBd  | Notes |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|------|------|------|------|------|------|-------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |      | Min. | Max. | Min. | Max. | Min. | Max. |       |

| tDSO                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output DIS skew              | ns   |      | ±5   |      | ±1   |      | ±0.5 | 1     |

| tLODSf                                                                                                                                                                                                                                                                                                                                                                                                                               | Output fall time (2.0–0.8 V) | ns   | _    | 40   | _    | 4    |      | 2    |       |

| tLODSr                                                                                                                                                                                                                                                                                                                                                                                                                               | Output rise time (0.8–2.0 V) | ns   | _    | 40   | _    | 4    | _    | 2    |       |

| NOTE — This is a skew measured at the 1.5 V threshold relative to the nominal time at which it is specified to cross it, defined<br>in terms of consecutive edges. For example, if two consecutive edges are nominally 5 ns apart, the length of time<br>between the time at which each will cross the threshold can be 5 ns apart, the length of time between the time at which<br>each will cross the threshold can be 5 ns ±tDSO. |                              |      |      |      |      |      |      |      |       |

Table 5-4 — S-SE output skew parameters

Allowable system skew is determined by the constraint that the sum of tDSI, the range of tDSO and the system skew shall not exceed nominal bit time. Thus, for DS-SE-01 links the system skew shall not exceed 5.5 ns.

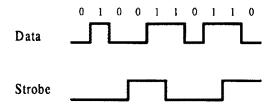

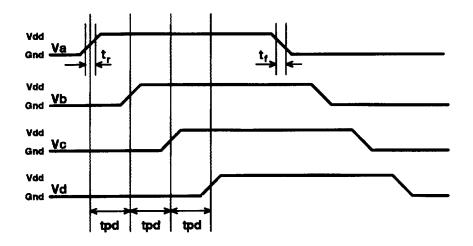

## 5.3.5 DS-SE link signals

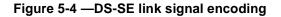

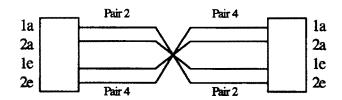

Information on a DS-SE link shall be transmitted using two connections, referred to as data and strobe respectively, in each direction. Each connection shall satisfy the electrical constraints specified in the previous subclause. The data line carries binary data values, and the accompanying strobe line changes state each time the next bit has the same value as the previous one (this does not correspond with the usual meaning of "strobe," which would be a signal that indicates every time that another signal is valid). By this means each DS pair carries an encoded clock, in a way that allows up to a full bit-time of skew-tolerance between the two connections. Figure 5-4 shows the form of signals on the data and strobe connections.

Since the data-strobe system carries a clock, the links are asynchronous; the receiving device synchronizes to the incoming data, This means that DS-SE (and DS-DE) links autobaud; the only restriction on the transmission rate is that it does not exceed the maximum speed of the receiver. This also simplifies clock distribution within a system, since the exact phase or frequency of the clock on a pair of communicating devices is not critical. It is not essential that both link outputs of one link connection should operate at the same speed, nor that a link output operate at a constant speed. A link output might choose to vary its speed of operation to reduce power consumption when there is no data to be transmitted, for example. The only constraint on the transmission rate is that the bit time limits given in table 5-3 are not violated, and that it is high enough to prevent a disconnect timeout being triggered (see 5.7.4.2).

A DS-SE link output transmits information on a pair of lines, and a DS-SE link input receives information on a pair of lines. A DS-SE link interface shall comprise a DS-SE link output and a DS-SE link input.

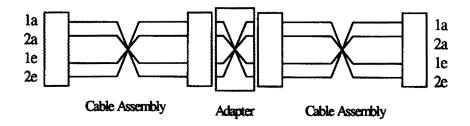

A device providing one or more DS-SE link interfaces shall identify the pins used for each link interface by a convention (using subscription where multiple links are supported) based on function and direction of transmission as shown in table 5-5.

| DS_SE_data_in    | For input of data to the device through the link interface    |  |

|------------------|---------------------------------------------------------------|--|

| DS_SE_strobe_in  | For input of data to the device through the link interface    |  |

| DS_SE_data_out   | For output of data from the device through the link interface |  |

| DS_SE_strobe_out | To output of data from the device through the fink interface  |  |

Table 5-5 — Identification of multiple link interfaces

A DS-SE link is constructed by connecting the DS\_SE\_data\_out and DS\_SE\_strobe\_out of one link interface to the DS\_SE\_data\_in and DS\_SE\_strobe\_in respectively of the other link interface, and vice versa.

The DS\_SE\_data\_out and DS\_SE\_strobe\_out of a link interface may be connected to the DS\_SE\_data\_in and DS\_SE\_strobe\_in respectively of the same link interface to create a loopback, e.g., for link testing.

# 5.4 DS-DE: physical medium

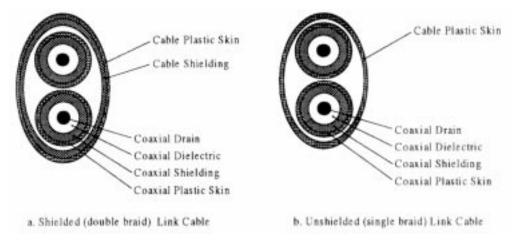

## 5.4.1 Link cable

A DS-DE link cable shall provide ten connections. Eight connections (in four pairs) shall support the eight signals in the DS-DE link; the ninth and tenth connections shall support an optional remote power facility.

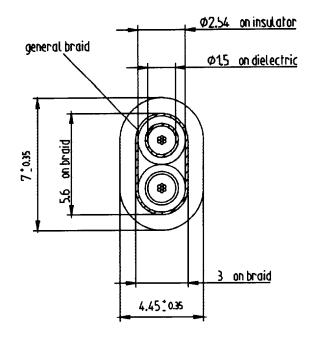

A recommendation for the DS-DE cable is given in annex M.

Each connection in the cable shall be color coded as given in table 5-6 and have the characteristics as given in table 5-7. Note that attenuation and skew budgets are given in 5.5.3 and 5.5.4. (See also 10.3.)

| Component | Conductor 1 | Conductor 2 |  |  |

|-----------|-------------|-------------|--|--|

| Pair 1    | Red         | Green       |  |  |

| Pair 2    | Brown       | Blue        |  |  |

| Pair 3    | Orange      | Yellow      |  |  |

| Pair 4    | Violet      | Gray        |  |  |

| Pair 5    | Black       | White       |  |  |

Table 5-6 — DS-DE cable color code

The link cable shall be clearly marked "IEEE 1355 DS-DE Link Cable."

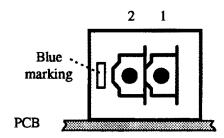

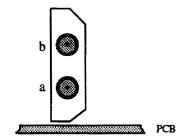

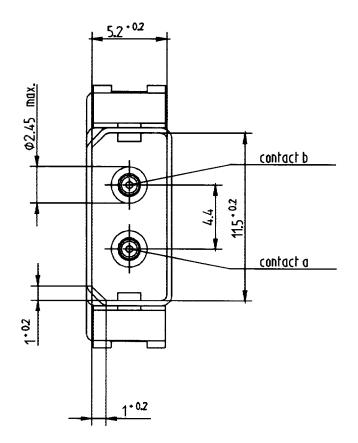

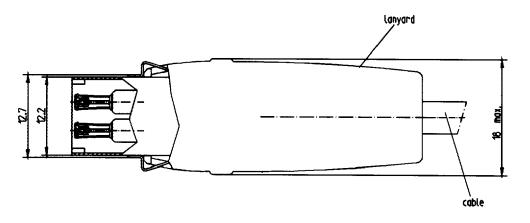

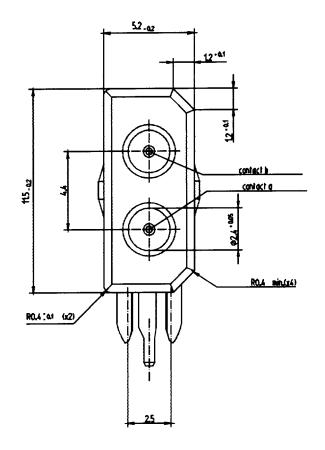

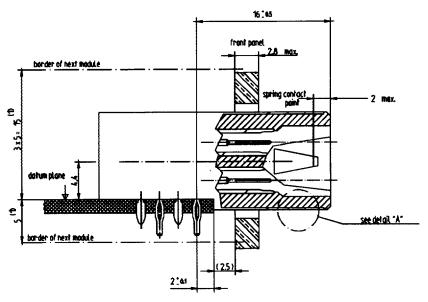

# 5.4.2 Connector

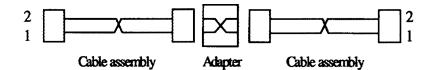

The connector system consists of a through-panel (fixed) connector and a cable-mounted (free) connector.

It provides the following features:

- a) A full duplex link connection per connector

- b) Option for multiple connections on the cable connector

- c) Complete screening

- d) Robust

- e) Latching

- f) Small size

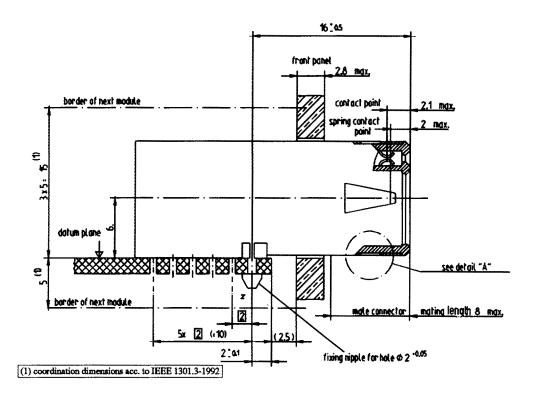

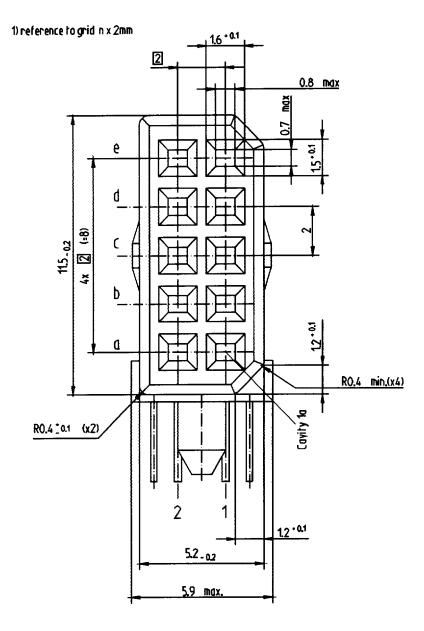

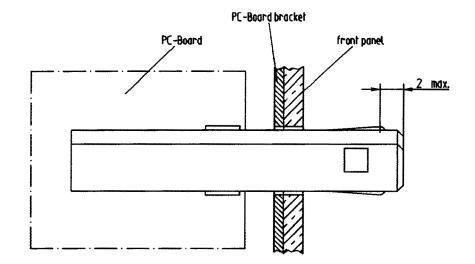

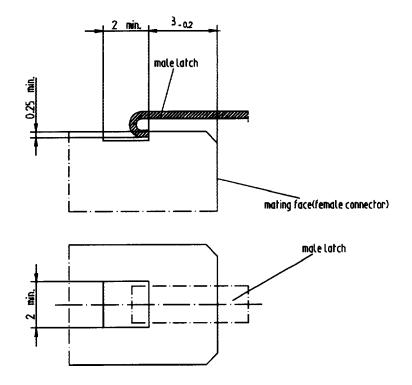

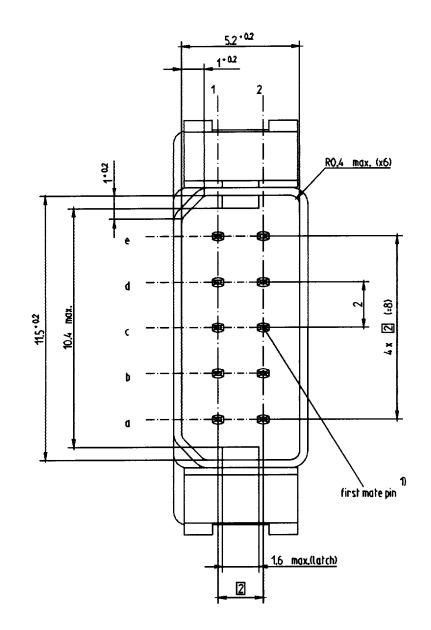

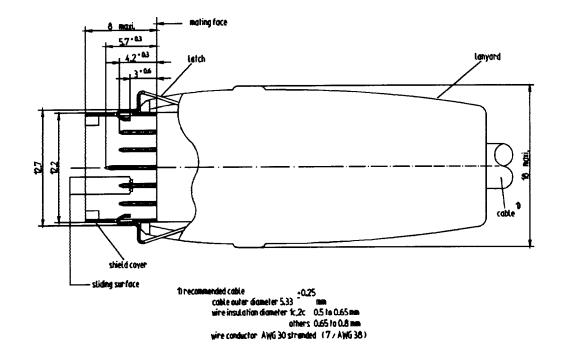

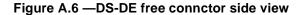

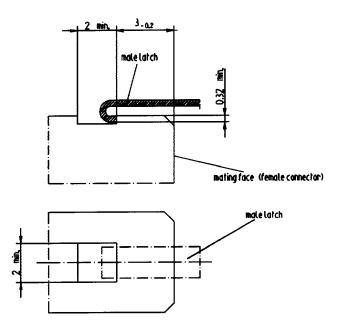

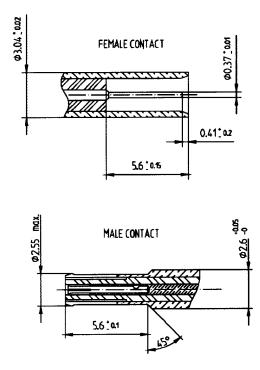

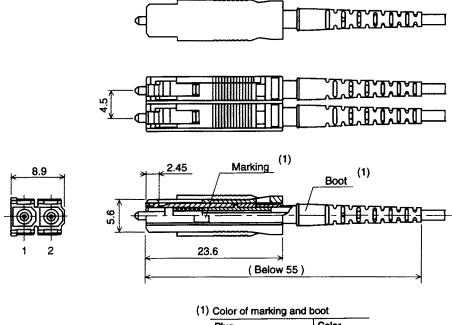

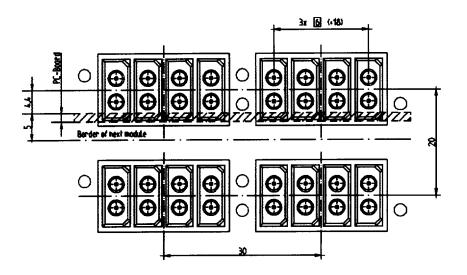

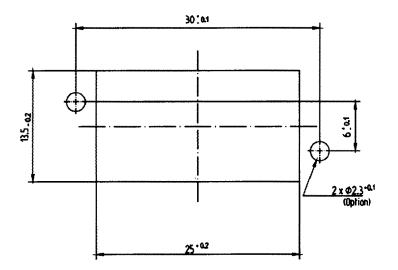

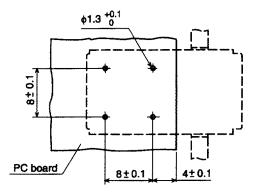

The DS-DE connectors shall be as specified in IEC 1076-4-107.

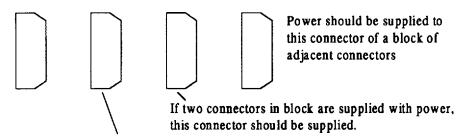

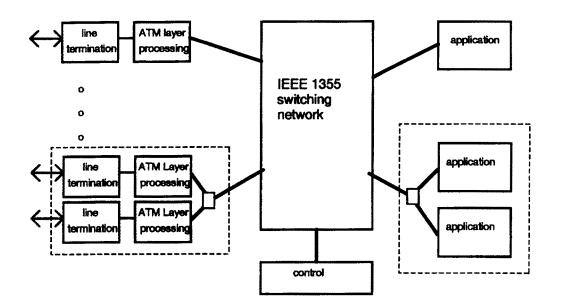

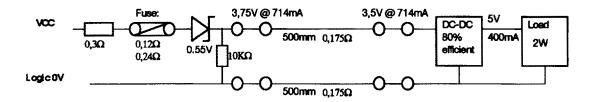

|                                           | Electrical characteristics                                                                                                                                                                         |